東レは10月23日、光通信技術(シリコンフォトニクス)に用いられる、InPをはじめとする光と電気を相互に変換する機能を持つ化合物半導体ベースの光半導体を、シリコン基板上に実装するための材料および技術を開発したことを発表した。同成果は、東レと子会社の東レ エンジニアリングによるもの。

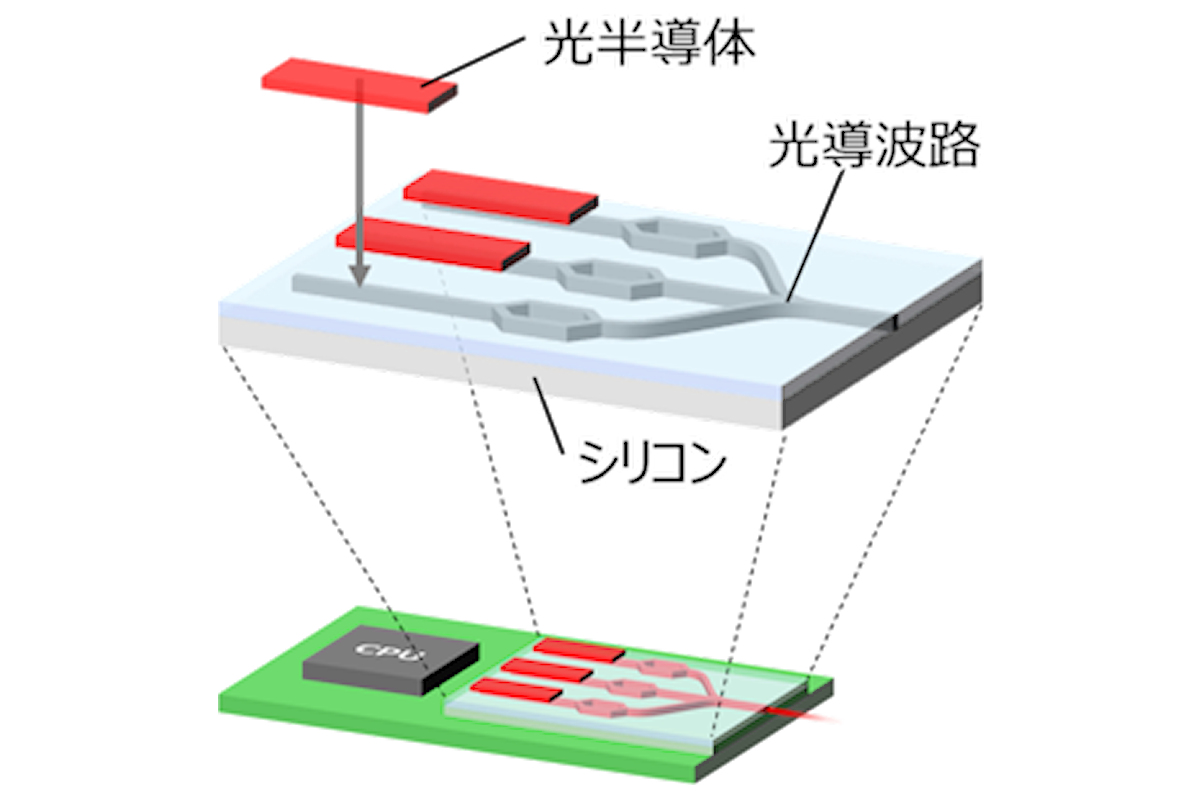

AIなどの進展による高速通信の拡大により、多量の電力消費を伴うデータセンターの増設が続いており、将来の電力需要の増大が懸念されている。そこで研究開発が進められているのが、電気通信よりも低エネルギー損失である光通信を、現在の長距離通信だけでなくデータセンター内の短距離通信にも適用しようという試みで、その実現には、シリコン基板上に光回路を形成するシリコンフォトニクスの活用が期待されているものの、InPなどのIII-V族化合物半導体を用いた光半導体をシリコン基板上実に大量かつ高速に実装する必要があり、そのための「マストランスファー技術」(一度に多量のチップを基板上に移送して、正確に配置する技術)の実現が求められている。

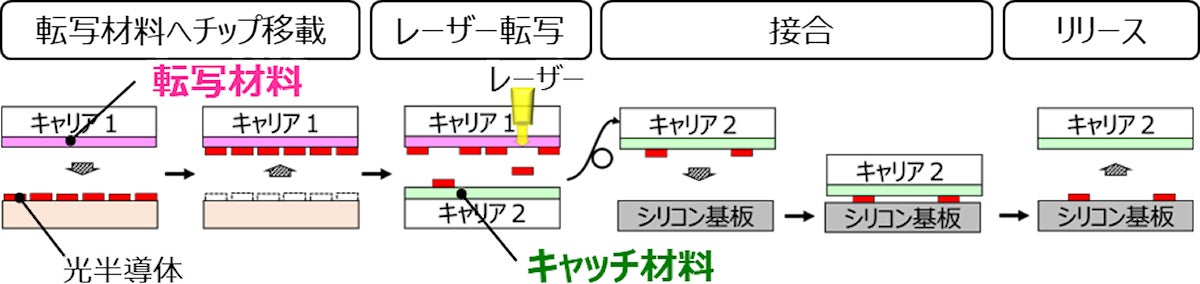

こうした市場背景を踏まえ東レでは今回、InPなどの光半導体をレーザーで高速転写するための転写材料、および転写されたチップをキャッチしてそのままシリコン基板上に直接接合が可能なキャッチ材料、およびその実装プロセス技術について、連携して開発することにしたという。

東レでは、すでにマイクロLED向けの転写材料を開発済みだが、今回用いられたInPベースの光半導体は640μm(縦)×90μm(横)、厚さ3μm以下と、一般的なマイクロLEDよりも縦横サイズが大きい一方で、厚さが薄いチップであり、破損のリスクがあったという。今回の取り組みでは、耐衝撃性制御によってチップを破損させることなく、1回のレーザー照射で転写可能な新規転写材料を開発。これにより、歩留まりと高スループットの両立が期待できるようになるという。

またキャッチ材料には、高速で飛んでくるチップをキャッチするだけはなく、その後のチップのシリコン基板への直接接合(薬品で洗浄後、プラズマで接合面を活性化して200℃以上で加圧)に耐え、その後、容易にリリースできることが求められていることから、長年培ってきた耐熱性高分子の設計技術および粘着性の制御技術を応用する形で、ニーズにマッチしたキャッチ材料を開発することに成功したとする。

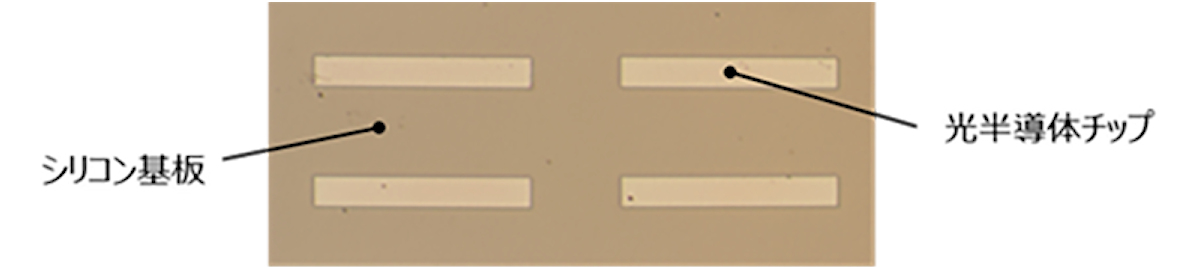

さらに、今回開発された材料を用いる形でのレーザー転写からシリコン基板上への直接接合までの一連のプロセスも開発、実証が行われたところ、現時点における接合後の位置精度は±2μm以内、回転ずれは±1度以内のレベルであることが確認されたとした。

なお、東レ エンジニアリングは、半導体実装用のボンダおよびレーザーマストランスファの設備技術を保有しており、その取り組みにより、光半導体の実装速度が向上。従来のフリップチップボンダでは1分間に約4個(同社調べ)ほどの実装速度であったが、今回の研究開発によって、その約1500倍となる1分間で6000個という高速実装が実現されたことから、データセンター内での光通信適用の加速が見込まれるとしている。今後について両社ではチップの動作検証を行いつつ、連携して実デバイスを用いた技術確立を2025年までに実現し、早期の量産適用を目指すとしている。加えて、位置精度のさらなる向上に取り組むと同時に、ほかの異種材料のチップやミリオーダーサイズの半導体チップのマストランスファーにも技術を展開していく予定としている。