毎年恒例の「PCI-SIG Developers Conference」が今年も6月12・13日にサンタクララのSCCC(Santa Clara Convention Center)で開催されている(PCI-SIG Developers Conference 2024)。

このPCI-SIG Developers Conferenceの初日に、これも恒例のPress Conferenceが行われたので、その内容をご紹介したい。ちなみに通例だとPCI-SIG ChairのAl Yanes氏が対応をされるのだが、今回はスケジュールが色々あったためか、Richard Solomon氏(Vice President and Compliant Chair)が担当された。

さて今年で設立から32年になるPCI-SIGであるが、流石に会員数はそろそろ頭打ちになってきた感がある(Photo01)。

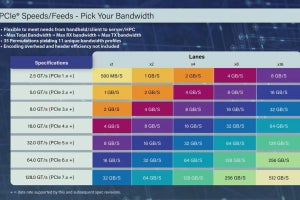

取締役会のメンバーは昨年から変更はない。このロードマップもお馴染み(Photo02)であるが、Solomon氏曰く「PCIeは決して最速のテクノロジーではない。それなりに高速な帯域を、リーズナブルなインプリメントコストで提供できる技術だ」としており、なのでこのロードマップは引き続き有効、という話でもある。

順調に開発が進むPCIe 7.0

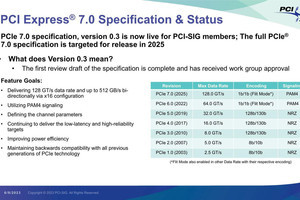

さて当然注目はPCI Express 7.0(PCIe 7.0)であるが、すでにVersion 0.5がメンバー会員に対してレビューに入った事が改めて説明された。通常だとここから0.7、0.9と進んで1.0に到達する訳であるが、そのVersion 0.5の詳細は当然明かせないとしながらも、少なくともVersion 0.5の段階では標準化が困難であるとされるほどの技術的な障壁は無く、標準化に向けて順調に推移している事を伺わせる説明が行われた。またComplianceに関しては、遂にこの2024年第2四半期にPCIe 6.0のPreliminary Compliance Testが開始され、2025年には広くテストが開始されることが説明された(Photo04)。

-

Photo03:PCIe 7.0は基本的にはPCIe 6.0のFLITモードをベースに信号速度を倍増させた格好である

-

Photo04:ちなみにPCIe 7.0は2028年である。まぁまだ未だにPCIe 6.0に対応したコントローラが殆ど無い(計画だけは色々あるが、実SiliconはTest用のモノが殆どである)事を考えれば、2028年でも十分間に合いそうな気はする

対応範囲が広いOptical

次がOpticalであるが、こちらもあまりUpdateは無い(Photo05)。

ただSolomon氏が強調したのは、Opticalが現在のCopperベースのモノを置き換えるという動きは特に考えておらず、PCIe 6.0についても将来的なOpticalに向けたECN(Engineering Change Notification)が年内に予定されているが、これはあくまでも現在のCopperベースの仕様を置き換えるのではなく、強化(enhancement)するに留まる、という話であった。

Opticalに関しては対応範囲が広く、それこそPluggable Optical TransceiverからCo-package Optics(つまりUCIeなどのChiplet間接続もターゲットに入る)までをカバーする事を「現在は想定している」という話だった。ただIEEEで言えば現在の作業はまだStudy Groupに相当するもので、レベルとしてはFeasibility Studyに近い。本格的な検討、つまりIEEEで言うTask Forceに相当するものは2025年に現在のPCIe 7.0の標準化が終わった後でスタートする、という話だった。逆に言えば、CopperベースのPCIe 8.0が出る可能性はかなり低いとPCI-SIGでは考えていることになる(個人的には妥当な判断だとは思うが)。

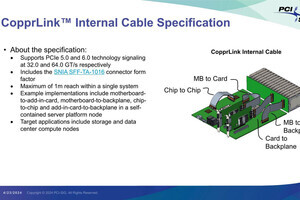

またケーブル接続については、先日発表されたCopprLinkの標準化が既に完了、今年後半にはPCI Express External Cablingの標準化も予定されている(Photo06)。

-

Photo06:Optical CableについてはすでにWIP(Work In Progress)である。というか、このスライドそのものが前回と全く一緒である

PCIeと生成AIの関係性

最後に、昨今ではAIについて何も語らないのはまずいらしく、無理やりPCIeを生成AIに絡めたスライドが出て来た(Photo07)が、これは流石に色々厳しい気がする。まぁシャーシ内での配線に絡んで、現状OCuLinkでは対応するスピードも帯域も低いので、これをCopprLinkで置き換えてゆくという形でAI向けServerの内部には入ってゆくと思うのだが……。

-

Photo07:現実問題として生成AIのラック間接続とかにはEthernetをベアで使うのが一般的になりつつあり、これをUltra Ethernetでフォローする方向になっているので、PCIe Cableの出番は無いように思う

ちなみに今年のCOMPUTEXでは電源メーカーがPCIe Gen 5.1を標榜していた(Photo08)。

実は2023年7月に、PCI-SIGはPCI Express CEM(Card Electromechanical Specification)Revision 5.1をリリースしており、電源メーカーはこれへの対応を謳っているわけだ。Base Specificationの方は5.0のままであり、その意味ではこの表記はあまり正確ではないと言える。ちなみに主な改定はCEM 5.0からのECNを取り込んだ格好で、この中には12VHPWR Cable Plug Update ECNが含まれている。要するに12VHPWRコネクタ(PCIeでは12V 2×6 connectorなどとも表記される)を仕様に含んだというだけで、それ以外は小変更に留まる。むしろ激しくVersion upされているのはPCIe 6.0の方で、Base Specificationは6.0が2022年1月に出た訳だが、2022年9月には6.0.1、2023年7月には6.1が出て、2024年2月には6.2がリリースされた。やはりPAM-4とかFLITの実装はそれなりに難易度が高い事を伺わせるような状況である。

なお、7月12日にはPCI-SIGによる“The Journey to CopprLink and Beyond: An Exploration of PCIe Cabling Solutions”というオンラインセッションが行われる。ここでまた何か新情報があったらレポートしたい。