ベルギーimecは、2月25-29日に米国カリフォルニア州サンノゼで開催されているSPIE主催の「Advanced Lithography + Patterning Conference 2024」にて、EUVプロセスをはじめ、EUVマスク、および高NA EUVリソグラフィを可能にするために用意された計算リソグラフィ、レジストと下地層の開発、EUVマスク、光近接効果補正(OPC)の開発、解像度フィールドステッチング、確率的欠陥の削減、および計測と検査の改善など、さまざまな研究成果に関する報告を行ったことを発表した。

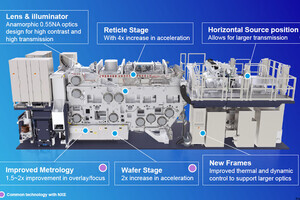

imecでは、これらの成果を踏まえ、最初のプロトタイプ高NA EUVスキャナを中心に(ASML本社敷地内に)構築された「imec-ASML High-NA Lab」にて高NA EUVプロセスを顧客が試用する準備ができたとしている。

imecのアドバンストパターニング、プロセス、材料担当シニアバイスプレジデントであるSteven Scheer氏は、「最初の高NA EUVスキャナ(TWINSCAN EXE:5000)は ASMLによって組み立てられ、今後数か月以内にimec-ASML High-NA EUVラボで顧客が試用することが可能となる。このHigh-NA EUV Labでの試用により、顧客は自社のファブで高NA EUV露光装置が実際に稼働する前に高NA EUVを使いこなす教育を開始することができるようになる。ASMLおよびimecの広範なサプライヤーネットワークと緊密に連携して、高度なレジスト材料、フォトマスク、計測技術、およびパターニング技術をタイムリーに利用できるようにすることがimecの役割である。高NA EUVの活用に向けたこれらのプロセスの準備が整っていることは、SPIE Advanced Lithography & Patterning Conference 2024で発表された25件以上の論文に示されている」と今回の研究成果が、そのまま顧客の半導体製造につながっていくものであると述べている。

また、材料とプロセスの面では、金属酸化膜レジスト(MOR)が金属ライン/スペースパターンにおいて依然として有利であるとimecは主張しており、EUV線量対収量低減の観点からMORの進歩をSPIE学会で紹介している。それによると特定の下地層の選択、現像プロセスの最適化、マスク吸収材の選択、マスクのバイアスおよびマスクの階調により、粗さの増加や確率的欠陥を引き起こすことなく、ラインとスペースの線量を20%以上削減することができたという。現在も線量の低減作業は継続しており、スキャナのスループット向上によりEUVのコスト削減が図れるようになるため、imec会員である先端半導体メーカー各社からは高く評価されているという。