「技術研究組合 最先端半導体技術センター(LSTC)」は2月9日、新エネルギー・産業技術総合開発機構(NEDO)の「ポスト5G 情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発(委託)」において、「Beyond 2nm及び短TAT半導体製造に向けた技術開発」と「2nm世代半導体技術によるエッジAIアクセラレータの開発」について採択されたことを発表した。

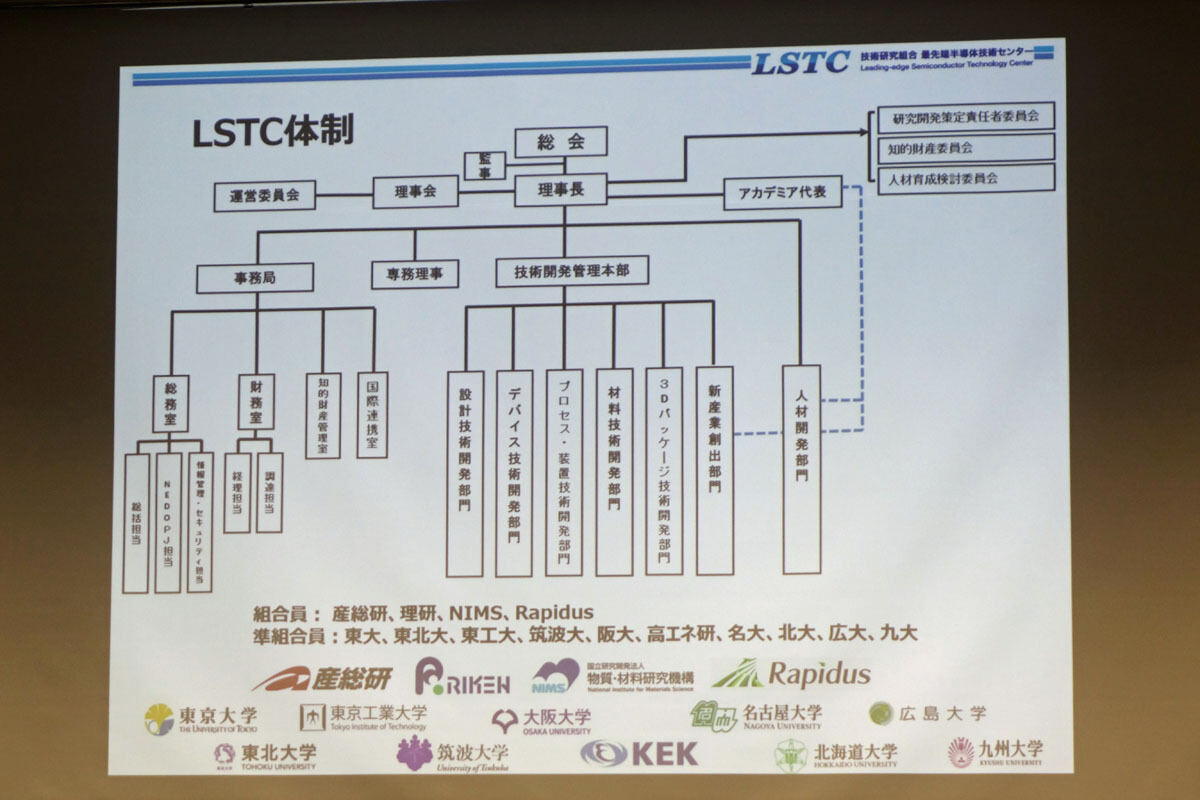

LSTC理事長の東哲郎氏は、LSTCの役割について「2nm以降の先端プロセスの開発」と表現。広範に日本の先端技術に関わっていく組織であり、そうした関係性から日本国内のみならず、米国、欧州の研究機関などと連携して、研究開発を進めていくとするほか、半導体製造装置メーカーや材料メーカー、ユーザー企業など幅広い企業とも連携を進める、日本の先端半導体研究の母体となる存在とすることに加え、先端半導体の研究開発のみならず、今後の半導体に携わる人材育成機能も持たせていくともし、この人材育成こそが重要となることを強調していた。

-

LSTCの体制。半導体製造に必要な各要素の開発に加え、人材育成も担うことが想定されている。2024年2月時点でLSTCは延べ17人ほどの組織とのこと、規模が大きくなっていくにつれて陣容を手厚くしていく必要があるとしている

2nmの先を見据えた研究を推進

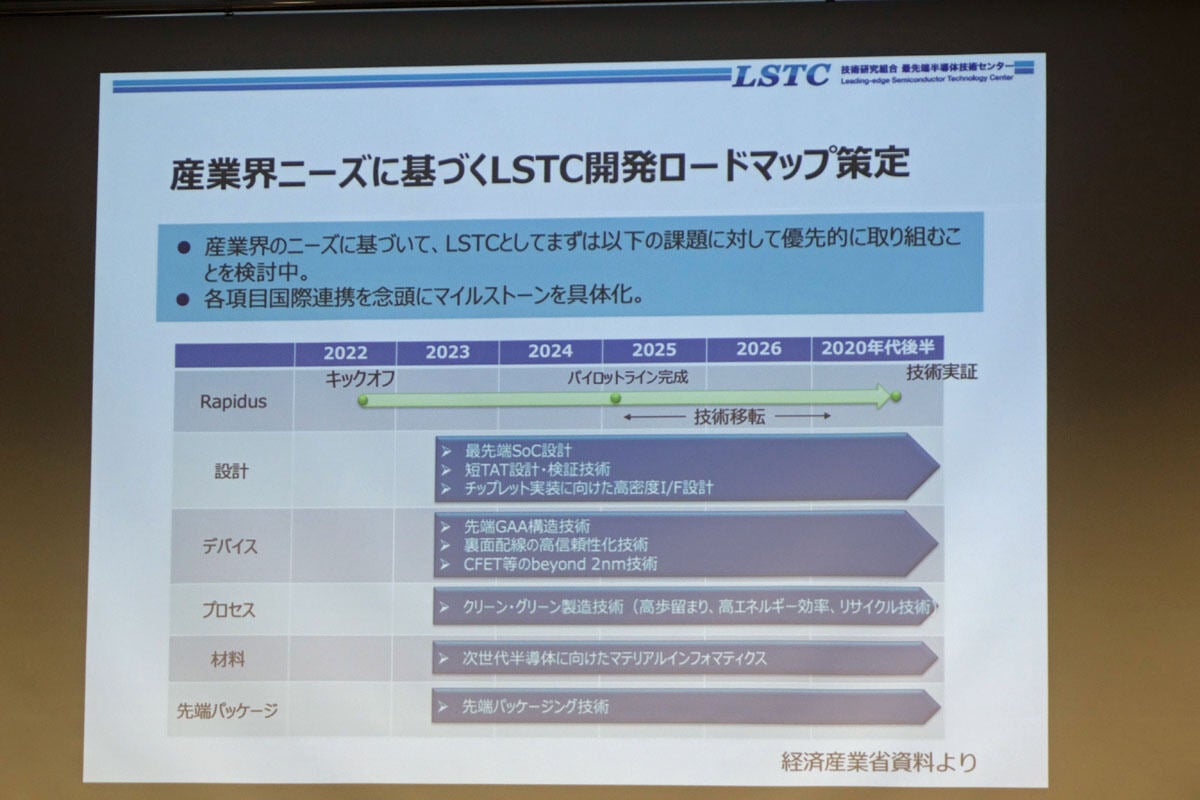

LSTCの当面の役割はRapidusが手掛けようとする2nmプロセスの量産技術の実現に向けて、パイロットラインの稼働と並行する形で、設計、デバイス、プロセス、材料、先端パッケージ、それぞれの部門が技術開発を進めていくこと。「Rapidusのパイロットラインの稼働が2025年春。2027年以降にRapidusの量産化、事業化が計画されており、それまでにしっかりとしたものを開発していくことになる」(東氏)とのことだが、その先にある裏面配線の高信頼性化技術やBeyond 2nm向けとなるCFETの実現に向けた要素技術開発、クリーン・グリーン製造技術などへの取り組みも視野に入れているとする。

この2nmの先の微細プロセス技術の要素開発がNEDOの採択1件目「Beyond 2nm及び短TAT半導体製造に向けた技術開発」となる。LSTCの技術開発管理本部長を務める昌原明植氏は「拡大する半導体市場をしっかり捕まえていくためには技術開発が重要。プロセスの微細化もそうだし、応用範囲の拡大も必要。そのためには短TATで半導体を製造していく必要がある。この両方を構築していくことで市場規模が拡大していき、結果として社会課題の解決にもつながる」と、短TATで半導体を製造する技術の重要性を強調。その実現に向けて、LSTCの組合員である産業技術総合研究所(産総研)、物質・材料研究機構(NIMS)、Rapidus、東京大学(東大)、東北大学、東京工業大学(東工大)、筑波大学、大阪大学(阪大)、名古屋大学(名大)、広島大学(広大)、九州大学(九大)のみならず、再委託先としてアプライドマテリアルズジャパン、キオクシア、グローバルウェーハズ・ジャパン、SUMCO、大陽日酸、Preferred Networks、リオン、共同実施先として横浜国立大学(横国大)、信州大学、電気通信大学(電通大)、豊橋科学技術大学(豊橋科技大)、芝浦工業大学(芝工大)、東京都市大学、明治大学(明大)、そして国際連携としてApplied Materials(AMAT)、CEA-Leti、imecと早々たる陣容で研究開発を進めていくとしている。

国際連携の役割としては、AMATが枚葉式製造装置の開発を、CEA-Letiとimecは2nm以降の微細プロセスの研究開発を共同で進める形を想定しているという。

ちなみに2nmプロセス以降の超微細プロセスの最初のターゲットは1.4nmプロセスとなる。2nmならびに1.4nmプロセス開発に必須となるEUV露光装置だが、Rapidusのパイロットラインを借りる形で開発を進めていくことが検討されているという。デバイス技術開発部門長の平本俊郎氏によると「1.4nmプロセスは2028年までには開発を完了させて、組合員に展開することを目指す」と意気込みを語るほか、半導体の微細化はそれ以降も続いていくことになるので、その都度、新たな研究開発プロジェクトが立ち上がっていくものと思われるという。

2nmプロセスを用いた高性能エッジAIアクセラレータを開発へ

NEDO採択の2件目の「2nm世代半導体技術によるエッジAIアクセラレータの開発」は、産業用ロボットや自動車、生活支援ロボットなどのエッジで活用されるクラウドを介さないで高度なAI推論処理を可能とするエッジAIアクセラレータを2nmプロセスを用いて開発しようというもの。生成AIを含む、エッジ推論応用処理用途の専用半導体を国際連携で開発していくことが想定されており、LSTCからは産総研、Rapidus、東大の3者が、国際連携としてTenstorrentが参画することが予定されている。

開発の方向性としては、CPUチップの開発にTenstorrentが関与。TenstorrentのRSIC-VベースのCPUがベースとなる予定だが、アクセラレータそのものはLSTCが独自開発することになるという。また、研究開発では3D ICによる統合アーキテクチャも開発するほか、TensorFlowやPyTorchなどAIフレームワークを活用できる汎用ソフトウェアの開発などを含めた、コンパイラ・ライブラリとシミュレータからなるソフトウェア開発基盤の構築なども行っていくとしている。

LSTCの新産業創出部門の大内真一氏によると、「Transformerモデル」を中核に、会話を認識させて、合成させることで、例えばクルマを会話で制御できるといったユーザーインタフェースの実現や、飲み物をこぼしてしまった際に、それを踏まえて片付けるところまでの一連のプログラムを生成するといったことなどが想定されており、従来のCNNにTransformerを加えることによる高性能化も期待できるため、自動運転制御などにも活用が期待できるとしている。

なお、2件の研究開発も2028年12月での終了を予定。Beyond 2nm世代向け半導体技術開発については170億円、2nm世代半導体チップ設計技術開発については280億円が事業費として予定されているという。また、人材育成に関しては文部科学省とも協議を進めているとのことで、互いに深く検討しあうという段階にあるという。