2023年は先端半導体プロセスとして3nmプロセスを用いた半導体デバイスの量産が進められた一方、2nmプロセスの実現に向けた研究開発が加速している。また、最近では1nmプロセスの準備も示唆されており、先端プロセスを扱うロジックファウンドリ間の競争が激化しつつあるとTrendForceが伝えている。

2nmプロセスは2025年の量産計画

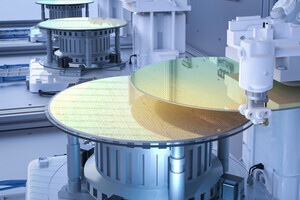

2nmプロセスの量産開始は2025年が予定されており、TSMC、Samsung Electronics、Rapidusなどの先端プロセスファウンドリ各社が実現に向けた取り組みを加速させている。TSMCは、2025年までにGAAを採用した2nmプロセスの実現を目指しているが、同プロセスは3nmプロセス(N3E)と比べ、15%の速度向上と最大30%の消費電力削減、そしてチップ密度の15%以上向上を果たそうとしている。すでに同社は2nmプロセスのサンプルをAppleをはじめとする大口顧客に渡しているという噂もある。

Samsungも2025年末までに2nmプロセスでの生産を開始する予定で、すでに大手顧客との協議を開始していることを明らかにしている。

日本での2nmプロセス量産を目指すRapidus(ラピダス)は、2025年の試験生産を経て、2027年までに量産対応を目指している。パートナーであるASMLは2024年内に北海道に技術サポートセンターを設立する予定で、Rapidus試作ラインでのEUV露光装置の立ち上げ支援や工場の立ち上げ、保守・点検支援などを行うとしている。

ただし、韓国の日刊紙である中央日報の日本語版が12月3日付で、同社の榎本貴男専務が11月に韓国釜山で開かれた半導体関連のイベントにて、韓国メディアに対し、「2028年から本格的に先端チップの試作品を生産するパイロットラインが稼働する」といった発言を行ったとし、計画が後倒しになる可能性を報じている。

1nmプロセスの実現時期は?

2nmプロセスの実現が視野に入った現在、半導体業界の注目は1nmプロセスの実現スケジュールに移っている。見通しとしては、2027年から2030年の間と見込まれている。最近、一部のメディアからは、Rapidus、東京大学、仏Letiが1nmプロセスのIC設計の基礎技術開発に向けて協力することで合意したと報じている。それによると、自動運転やAIの性能向上に向けた1nmプロセス半導体デバイスの供給体制確立を目指し、人材交流や技術共有を2024年より開始する予定だという。また、日本としては、1nmプロセスでのIBMとの協業も検討しているという。

TSMCとSamsungも1nmプロセス実現を目指した動きを見せているが、TSMCは台湾に1.4nmプロセス対応工場を建設することを計画していたものの、10月に当初想定していた用地の取得を断念した模様で遅れる可能性がでている。Samsungは2027年末までに1.4nmプロセスを立ち上げることを目指しており、トランジスタあたりのナノシートの数を増やすことで性能と消費電力を向上させ、電流フローの制御強化とリーク電力の低減を掲げているという。

Intelは4年で5世代の微細化を実現できるのか

TrendForceの報告では現状、市場シェアがそこまで大きくないIntelについては触れないが、同社は現在、「4年で5世代の微細化」を実現することで、競合ファウンドリに技術的に追い付き、追い越すことを目指している。微細化の段階を踏んでいく手法は正道であるが、それをこのスケジュール通りに実現できるかは未知数である。3nmプロセス採用の次世代CPUの一部をTSMCに委託したという話もTSMCの台湾サプライチェーン情報として出回っている。

imecがロジックプロセスのロードマップを後ろ倒し

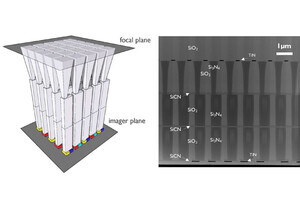

ベルギーimecが11月に東京で開催したイベントで、ロジックプロセスのロードマップの最新版が公開されたが、実は従来公開していたロードマップよりすべての技術ノードが1年後ろ倒しされていた。

3nmプロセスの生産開始時期を2022年としていたが、それが2023年にずれこんだためで、最新ロードマップではそのずれを織り込んで、それ以降の予想を1年ずつ後退させている。

プロセスの微細化は物理限界に近付きつつあり、そうした中での超微細構造を実現するためには、課題解決に必要な時間をかなり要する見込みであるため、よほどの破壊的イノベーションが登場しない限り、今後もこのロードマップどおりには微細化が進まない可能性もある。とはいえ、imecの新たなロードマップでは、sub-2A(2オングストロム未満)が追加されており、その実現性はともかく、imecとしてあくまでも「ムーアの法則」を延命させる意気込みを感じさせるロードマップとなっている。