imecは、米国サンフランシスコにて開催されている半導体の国際学会「IEDM 2023」において、招待講演3件、フォーカスセッション特集論文2件、主催者が選んだ注目論文1件を含めた合計16件の論文(共著を含む)が技術講演セッションで発表されることを明らかにした。

分野としても最先端ロジック技術、メモリ技術、相互配線および3D集積技術、5Gワイヤレス技術、イメージセンサ向けフォトニクス技術、バイオエレクトロニクスと多岐にわたっており、imecでは16件のうち、画期的な進歩をもたらす内容として3件の成果をプレスリリースとして12月11日付(欧州時間)で発表した。

より小さな画素で高解像度を実現するイメージセンサ技術

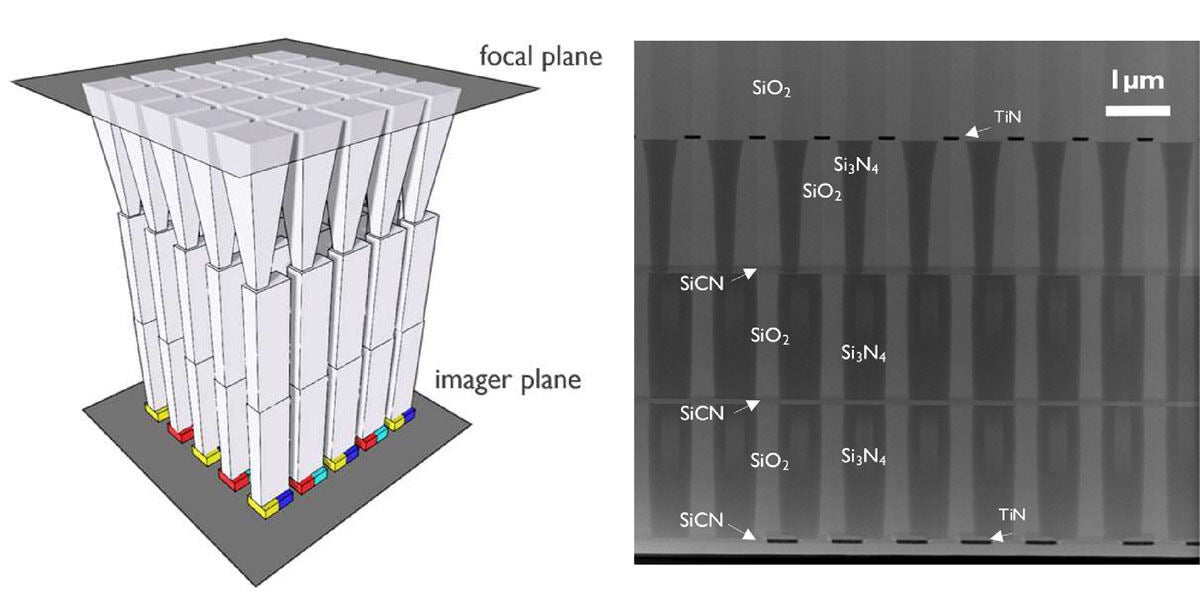

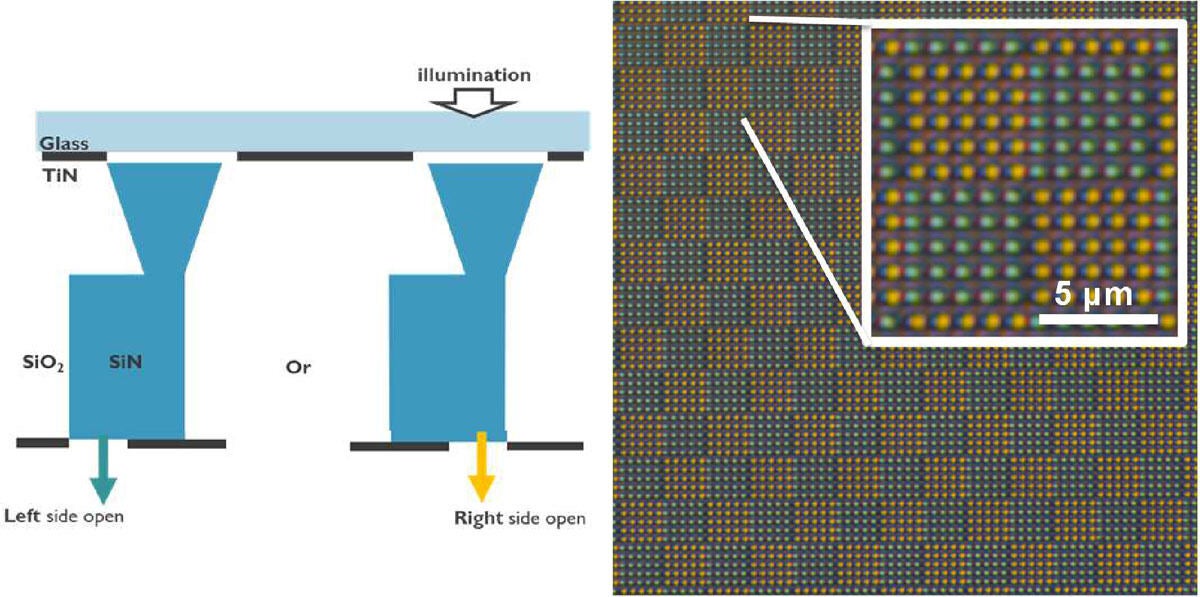

1つ目は「Wafer-level-integrated vertical-waveguide sub-diffraction-limited color splitters(ウェハレベル集積型垂直導波路サブ回折限界カラースプリッタ)」というタイトルで論文発表されたもの。

次世代CMOSイメージセンサには、より小さなピクセルとより高い解像度が求められるが、ピクセルが小さくなるほど取り込む光が少なくなるため、解像度を上げるのは困難という課題がある。

より多くの光を捉える方法の1つとして、入射光をさまざまな色に対応するさまざまな波長に分割し、人間の目の色感度に合わせてそれらの波長を調整する方法があり、imecのイメージセンサ研究チームでは今回、300mmウェハ上の標準的なBEOLプロセスを用いて、サブミクロンのピクセルサイズでこれを実現できる新たな方法を発表したという。

具体的には、SiO2マトリックス内にSi3N4マルチモード導波路のアレイを構築。各導波路は、異なる周波数の光を対称モードと非対称モードの両方に分割し、導波路内を異なる方法で伝播するため、特定の周波数で2つのモード間に独特の「うなり」パターンが生ずる。このパターンは特定の色を表現するために使用される。 研究者らは、この技術により、より高い信号対雑音比、優れた色品質がもたらされるとともに、前例のない空間解像度を実現し、ハイエンドカメラのパフォーマンスを向上させる道を切り開く説明している。

imecの主任技術スタッフであるRobert Gehlhaar氏は、「この技術は標準の300mmウェハプロセスと互換性があるため、スプリッタをコスト効率よく製造できる。これにより、すべての入射光子とその特性を検出するという最終目標に向けて、高解像度イメージセンサのさらなるスケーリングが可能になる。我々の目標は、回折限界の解像度を備えたカラーイメージングの将来の標準になることである」と抱負を述べ、imecの最終的な目標はすべての入射光子を検出することであるとしている。なお、この論文は、IEDMプログラム委員会が選んだ注目論文の1つにも選ばれている。

200mmのシリコンウェハ上にAlN/GaNのMISHEMT形成に成功

2つ目は、「High Performance mmWave AlN/GaN MISHEMTs on 200 mm Si Substrate(200mm Siウェハ上における高性能ミリ波AlN/GaN MISHEMT)」というタイトルで論文発表されたもの。

この研究でimecは、AlN/GaN MISHEMT(Metal-Insulator-Semiconductor HEMT)を200mmシリコンウェハ上に形成。28GHzで動作しながらハイパワーでエネルギー効率の高いトランジスタを実現し、ほかのGaN MISHEMTよりも高性能であること、ならびにシリコン基板を用いることで、工業化に際したコスト面でのメリットを打ち出すことも可能としたという。imecでは、5Gが最適な用途と考えているとする。

そして3つ目は「Scaling the SOT track – A path towards maximizing efficiency in SOT-MRAM(SOTトラックを縮小する - SOT-MRAMの効率を最大化する方法)というタイトルで論文発表されたもの。

この研究では、高い性能を示す微細SOT-MRAMデバイスの発表が行われる。具体的には、ビットあたり100fJ未満のスイッチングエネルギーと1015回を超えるデータ書き換え耐性が得られたとのことで、不揮発性SOT-MRAMテクノロジーがラストレベルキャッシュメモリアプリケーションに一歩近づいたと主張している。

なお、このほかIEDM 2023ではimecの研究者による招待講演として、「Backside Power Delivery: Game Changer and Key Enabler of Advanced Logic Scaling and New STCO Opportunities(裏面電源供給:先端ロジック微細化を可能にするゲームチェンジャで、システム-プロセス技術同時最適化の新たなチャンス)」、「3D Stacked Devices and MOL Innovations for Post-Nanosheet CMOS Scaling(ポストナノシートスケーリングのための3次元積層デバイスとMOL(中工程)イノベーション」、「Ultimate Layer Stacking Technology for High Density Sequential 3D Integration(高密度逐次3次元集積のための究極的な積層技術)」(発表は共著者であるSoitec)の3件の発表が行われる予定でもある。