NEDOとキオクシアは、受信信号からクロック信号のロック位置を検出するにあたり、コンパレータをNRZモードで動作させることにより、特定の遷移点を見て受信データを誤認することがなくなり、誤ロックが回避できることを発見したとする。

これを利用して、まずコンパレータをNRZモードで動作させてクロック信号を正しい位置でロックさせた後、コンパレータをPAM4モードへ変更することで、PAM4信号を正しく受信することが可能となったという。

具体的には、最初にコンパレータをNRZモードで動作させた際は、受信機のイコライザ、可変利得増幅器、コンパレータのパラメータを最適化する制御が行われ、クロック信号を正しい位置でロックさせる。そしてコンパレータをPAM4モードに切り替えた後にも、イコライザおよびコンパレータのパラメータを最適化する制御を行うことで、最適な位置にクロック信号をロックさせるという。

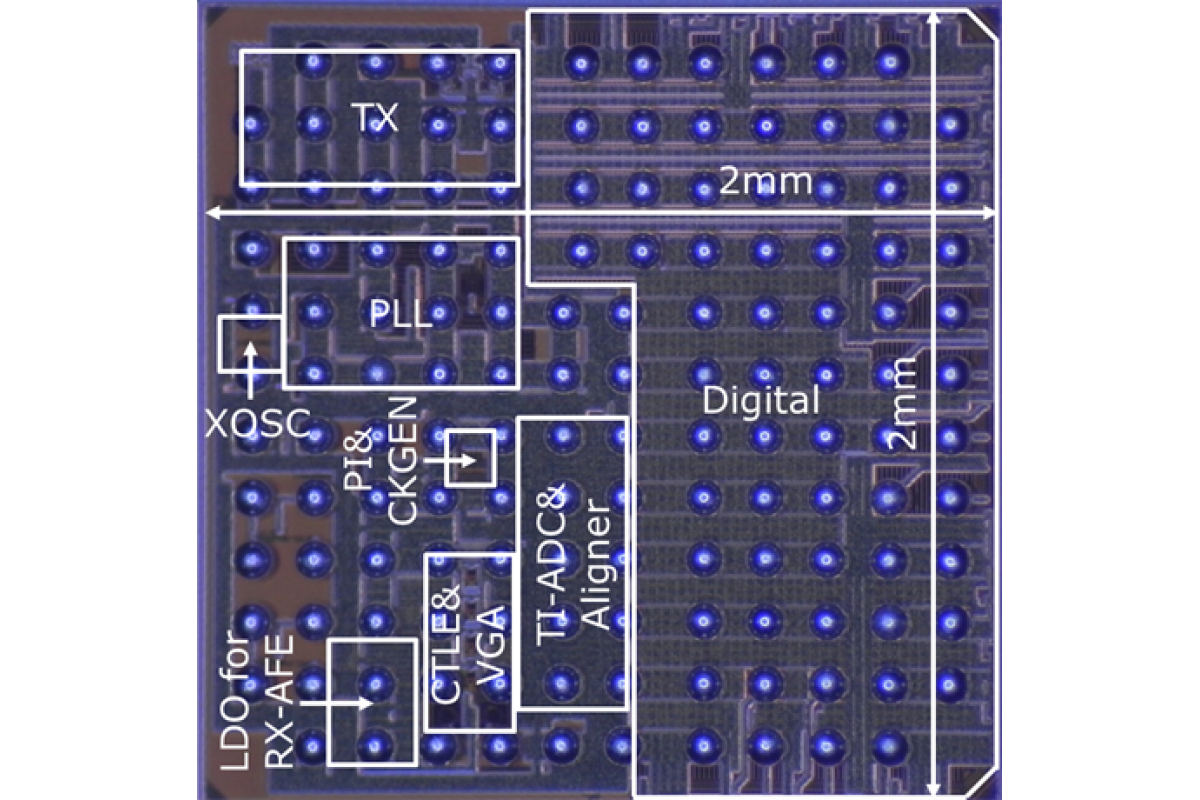

試作されたトランシーバの性能評価の際は、トランシーバの送信機で生成された56GbpsのPAM4信号を一度チップの外部に取り出し、ケーブルを用いてチップ内の受信機にループバックすることにより、56Gbpsでの動作確認が行われた。試作したトランシーバにおいて、今回考案された誤ロック回避機能の有効性が確認されたとする。

なお、キオクシアは今後、NEDOの事業で研究開発中の「メモリデイジーチェーン技術」に今回の成果を活用し、広帯域大容量フラッシュメモリモジュールの開発を進めていくという。そして消費電力40W以下、容量5TB以上、帯域64GB/s以上のメモリモジュールの実現を目指すとしており、これにより、5Gネットワーク内に同メモリモジュールが実装されることで、モバイル・エッジ・コンピューティング・サーバーにおけるビッグデータ解析が可能となり、IoTをはじめとする産業のスマート化が期待されるとしている。