2022年6月にハワイで開催され、7月5日時点でオンデマンド放映が行われている「2022 IEEE Symposium on VLSI Technology&Circuits(VLSIシンポジウム)」にて、ASMLのプレジデント兼CTO(最高技術責任者)であるMartin van den Brink氏が、「2020年代以降の最先端半導体製造への総合的なパターニング」と題した講演を行い、「半導体のイノベーションによる価値創造は、当面、減速しないだろう。ムーアの法則の限界がささやかれているが、高NA EUVリソグラフィの実用化により、予測可能な範囲の将来(2030年代)にわたってムーアの法則は継続する」との見方を示した。

量産適用された半導体露光技術は、過去35年以上にわたり、g線(波長436nm)からi線(同365nm)、KrF(同248nm)、ArF(同193nm)、液浸ArF、EUV(同13.5nm)を経て、高NA EUV(13.5nm)に至り、解像度を向上させてきた。

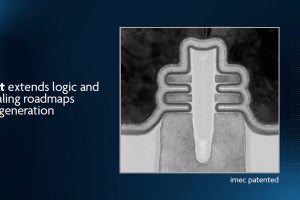

これにより、デバイスの微細化が実現され、先端領域ではEUVの適用がロジック/MPUからDRAMにも広がりを見せているものの、製造されるデバイスの種類によってEUVからi線に至るまでさまざまな露光技術を最適に組み合わせて活用されている。

Van den Brink氏は、ArF液浸露光を用いたマルチパターニングに替えてEUV露光によるシングルパターニングを採用することで

- プロセス簡略により欠陥密度低減が可能

- 製造サイクル短縮により急速立ち上げおよび高歩留まりが可能

- リソグラフィ・エッチング工程を繰り返す必要がないのでパターニングコスト削減が可能

- ファブスペースが削減しファブとしての出荷数量増加

などの利点があるとし、EUVリソグラフィの優位性を強調した。