SEMICON KOREA 2022は2月9日~11日にかけて、韓国のソウルでリアルの展示会が、また9日~25日にかけてバーチャル・オンデマンドで講演会が開催された。

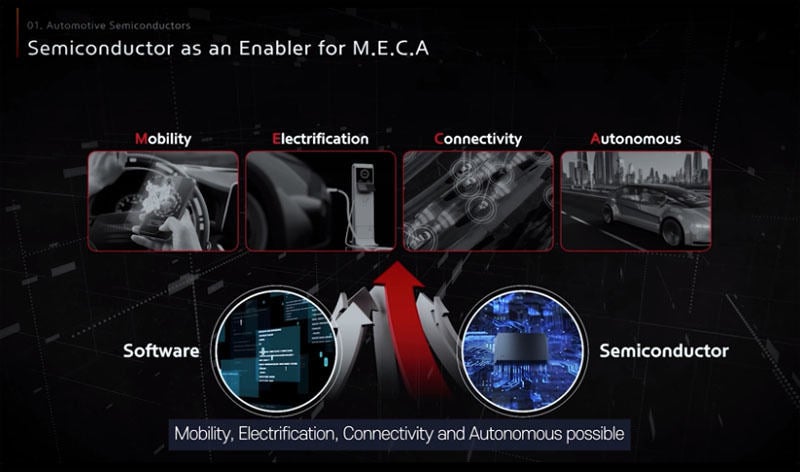

その基調講演の1つに、韓Hyundai Group(現代グループ)の自動車部品メーカーであるHyundai MobisでCEOを務めるSung Hwan Cho氏が登壇し、「Semiconductors in the Future of Mobility(モビリティの将来を支える半導体)」と題して講演した。

同氏は、将来のクルマのトレンドは、

- Mobility(移動の手段)

- Electrification(電動化)

- Connectivity(通信による接続)

- Autonomous(自動運転化)

の4つの単語で表されるとした。この「M.E.C.A.」を実現するためのソフトウェアがコアであり差異化要素となるが、その機能を存分に発揮するためには先端の半導体が必要であり、M.E.C.A.の実現のためには高機能な半導体が必須であるCho氏は強調した。

車載半導体のキープレーヤーとして、同氏はNVIDIA、イスラエルMobileye、Teslaの名前を挙げているほか、車載半導体開発に注力するTier1として、デンソー、ルネサス エレクトロニクス、独Boschなどを挙げており、将来のモビリティ向け半導体で要求されるのは、「高性能もしくは性能の最適化」、「小型化(多数の個別チップのSoC化)」、「低コスト化」、「効率的な開発サイクル」の4項目であると指摘した。

併催の技術シンポジウムで、各社が最新技術を披露

SEMICON KOREA 2022では、併催のSEMI TECHNOLOGY SYMPOSIUM(STS)も2月25日までオンデマンド形式で開催されていた。今回のSTSは、リソグラフィ技術、材料およびプロセス、デバイス、プラズマエッチング技術、CMPおよび洗浄技術、パッケージングおよびインターコネクトの6セッションで構成されていた。

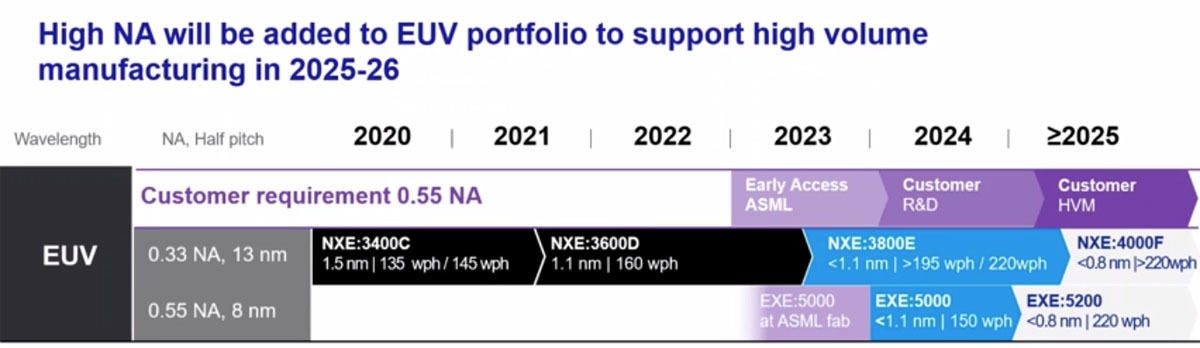

「リソグラフィ技術」セッションでは、キオクシアがナノインプリントリソグラフィの開発状況の報告を行った。2050年のカーボンニュートラル実現に向けて潜在的可能性のある技術であることを強調していたが、実用化は不透明である。また、ASML Koreaが高NA(NA=0.55) EUVリソグラフィ量産機に至るロードマップについての説明を行った。主要顧客は、2023/24年に高NA EUV試作機、2025年に量産機の出荷を求めており、その時間軸に沿って順調に開発を進めているという。従来のEUV量産機(NA=0.33)に関しても、2023年にはスループットを毎時220枚まで上げる計画だという。このほか東京エレクトロンが、MOR(メタルオキサイドレジスト)およびCAR(科学増幅型レジスト)を用いたリソグラフィプロセスについて紹介をした。

「CMPおよび洗浄技術」セッションでは、Samsung Electronicsが、ディープラーニングアルゴリズムを適用したCMPプロファイル予測を、SK Hynixが、3D NANDプロセスにおいてリン酸でシリコン窒化膜をエッチングする際にシリコン窒化膜とリン酸との反応でシリコン酸化膜層端に酸化膜が堆積する現象について、東京エレクトロン九州が、ウェハ洗浄によるパーテイクルの除去技術について解説を行った。

「パッケージング技術」セッションでは、Samsungが「チップレットパッケージング技術」について紹介した。スケーリングの速度が鈍化し、トランジスタコストが増加する中、チップレット、2.5Dおよび3Dアプローチを含む異種積層が、有望な代替手段とされるようになっている。

高性能チップのサイズは1レチクルサイズまで拡大しており、最先端プロセスの製造コストは上昇し続けている。そのため、そうした課題を解決するべく2.5Dをはじめとした費用対効果の高いさまざまなチップレットパッケージソリューションが提案されている。

チップレット導入の主な利点は、歩留まりの向上による低コスト化と信号伝送距離の短縮による性能向上であるが、Samsungの試算によれば、150平方mm以上のデバイスではチップレット化した方が低コストになるという。

このほか、半導体パッケージ基板製造用の先端絶縁材料のサプライヤとして知られる味の素は、次世代パッケージングのための絶縁材料「Ajinomoto Build-up Fil(ABF)」についての紹介を行った。同社は、さらに薄い誘電体層と細線および空間用のビルドアップ材料の開発が進んており、10μm未満の微細ビアを生成することができ、かつ熱膨張係数(CTE)が低く、FO-WLP/PLPのヤング率が低い成形フィルムも開発しているという。

また、KLA傘下のSPTSは、Wafer to WaferやDie to Waferなどの費用効果が高く信頼性の高いハイブリッドCuボンディングを可能にするプラズマエッチングおよびCVD技術について発表した。高価なCMPプロセスを削減するシリコンエッチングプロセス、ハイブリッド結合強度を改善するための最適化されたSiCNフィルムの低温PECVD、結合ダイ間のギャップフィルのための厚い酸化物の低温PECVD、および同社独自のプラズマダイシングを用いることにより、パーテクィルの減少、ストレス耐性の向上、ボイドの低減などにより結合スタックの歩留まりとデバイスの信頼性を高めることができるという。