Intelの共同創業者であるGordon Moore氏が1965年に提唱したいわゆる「ムーアの法則」は、さまざまな技術革新を取り入れることで過去50年を超えて存続してきたが、Intelは2025年以降も、継続していくことが可能であるとして、12月11日~15日にかけて米国で開催された半導体のデバイス技術とプロセス技術に関する世界最大級の国際学会「IEDM(International Electron Devices Meeting)2021」にて複数の最新技術を公開した。

-

ムーアの法則は今も生き続けている。EUVリソグラフィ、新しいトランジスタの構造、新しい電力供給技術、先進実装技術などの多くの技術革新によりこれからもムーアの法則は生き続ける (出所:C.H. Lin、Intel。IEDM2021ショートコース(短時間講義)配布資料より、元はIntel Innvation Day 2021での発表資料)

パッケージング密度の向上技術

IEDM2021にて同社が報告した中の1つが、ハイブリッドボンディング接続の設計、プロセス、およびアセンブリの課題に対するソリューションに関するもの。パッケージングにおけるインターコネクトの密度は今後10倍以上となることが想定されており、同社でもすでに10μm未満のバンプピッチを可能にするFoveros Directを導入する計画を発表している。同社は、ハイブリッドボンディング/チップレットエコシステムを実現するための新しい業界標準とテスト手順の確立も進めているとしている。

次世代トランジスタによるスケーリング改善

また、トランジスタのスケーリングに関しては、次世代として導入予定のゲートオールラウンド方式の「RibbonFET」(同社独自の呼称)以降のムーアの法則の継続的な進歩に向け、複数のCMOSトランジスタをスタックするアプローチを取り入れることで、単位面積当たりのトランジスタ数を増大させ、ロジックスケーリングの最大30~50%の改善を目指すとしている。

さらに、オングストローム時代に向けて、数原子ほどの厚みの2次元(2D)材料の活用による新たなトランジスタの作成方法などの開発も進めているとしている。

シリコンウェハに新たな機能を追加

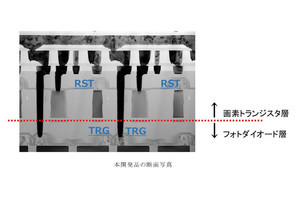

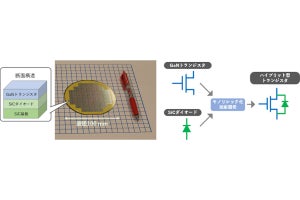

トランジスタ性能を向上させるアプローチのほかにも同社は、シリコンに新たな機能をもたらす研究についても報告している。例えば、300mmウェハ上のシリコンベースのCMOSに、GaNベースの電源スイッチを内蔵することで、電力効率の向上を実現したことを明らかにした。

もう1つの進歩は、ゲームからAIまで、ますます複雑化するコンピューティングアプリケーションに対応するために、より多くのメモリリソースを提供できる、次世代の組み込みDRAMテクノロジに対応する強誘電体材料を使用した低遅延の読み取り/書き込みを報告している。

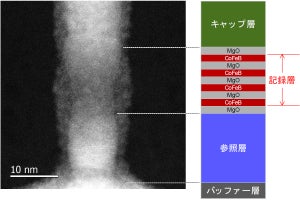

室温動作の磁電スピン軌道(MESO)ロジックデバイス

このほか、同社は次世代のコンピューティングの実現に向け、室温動作が可能な実験的な磁電スピン軌道(MESO)ロジックデバイスの実験的な動作を実証したことも報告したほか、imecと協力してスピントロニクス材料の研究を進めていること、拡張可能な量子コンピューティング実現に向けた完全な300mm量子ビットプロセスフローの紹介なども行っている。