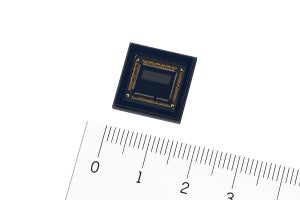

ソニーセミコンダクタソリューションズは12月16日、2層トランジスタ画素積層型CMOSイメージセンサ技術の開発に成功し、同成果の詳細を半導体のデバイス技術とプロセス技術に関する世界最大級の国際学会「IEDM(International Electron Devices Meeting)」にて発表したことを明らかにした。

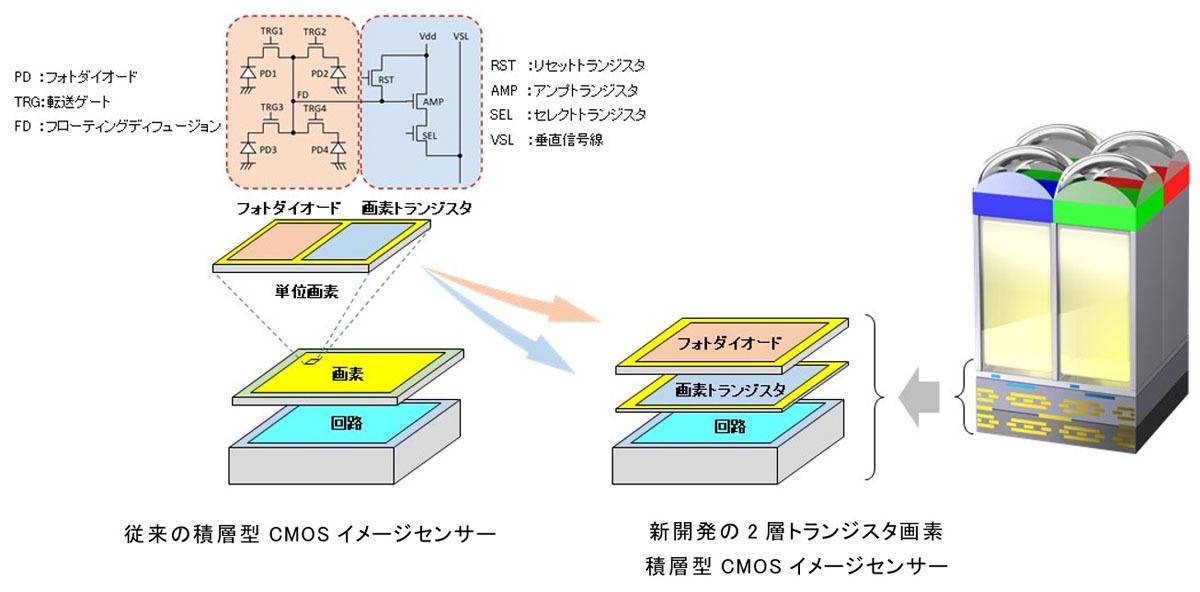

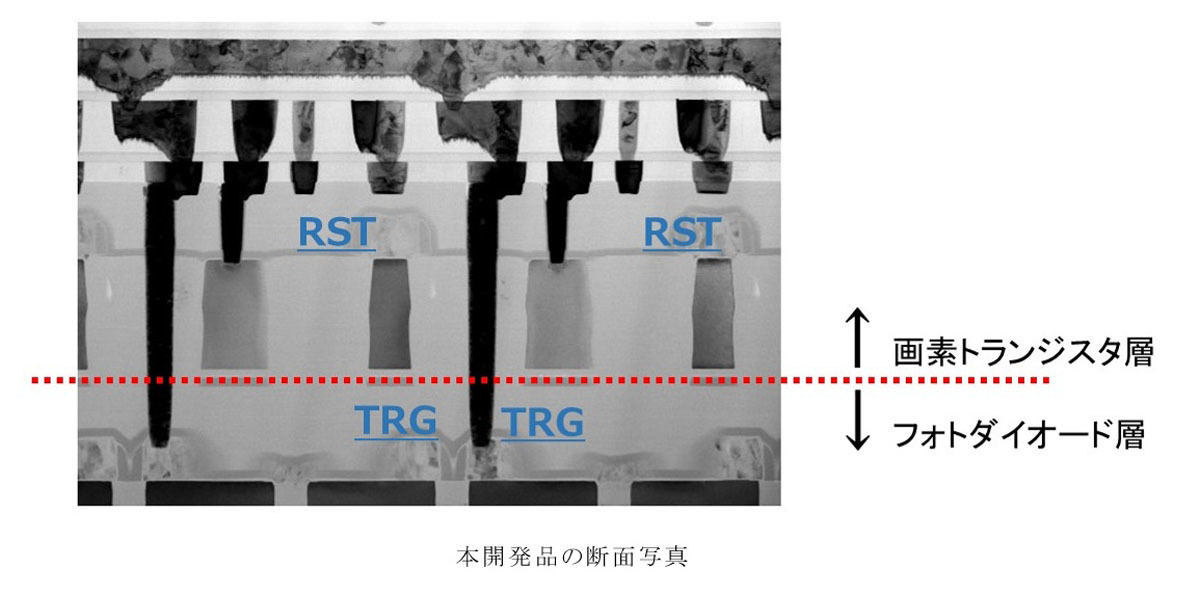

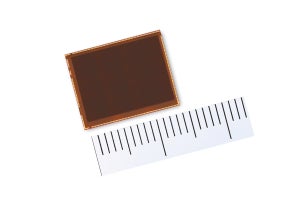

積層型CMOSイメージセンサは、裏面照射型画素が形成した画素チップと信号処理回路を形成したロジックチップとを重ね合わせたもの。画素チップは、光を電気信号に変換するフォトダイオードと、信号を制御するための画素トランジスタを同じ層に配置する構成であったが、今回開発された技術はフォトダイオードと画素トランジスタの層を別々の基板上に形成し、積層することで、それぞれに最適化を施した構造の採用が可能となり、同社の実験では従来比約2倍の飽和信号量を実現することに成功したという。

また、転送ゲート(TRG)以外のリセットトランジスタ(RST)、セレクトトランジスタ(SEL)、アンプトランジスタ(AMP)などの画素トランジスタをフォトダイオードとは別の層に形成したことで、アンプトランジスタサイズの拡大が可能となり、夜景などの暗所撮影時に発生しやすいノイズを低減させることにも成功したともしている。

同社では、ダイナミックレンジ拡大とノイズ低減を実現することが可能となる今回の技術を活用することで、逆光などの明暗差が大きいシーンでも白飛びや黒つぶれがなく、室内や夜景などの暗いシーンでもノイズの少ない高画質な撮影が可能となるとしており、将来のスマートフォンでの撮影などのさらなる高画質化を実現していきたいとしている。