Efficieraを搭載する半導体はどの程度の性能なのか?

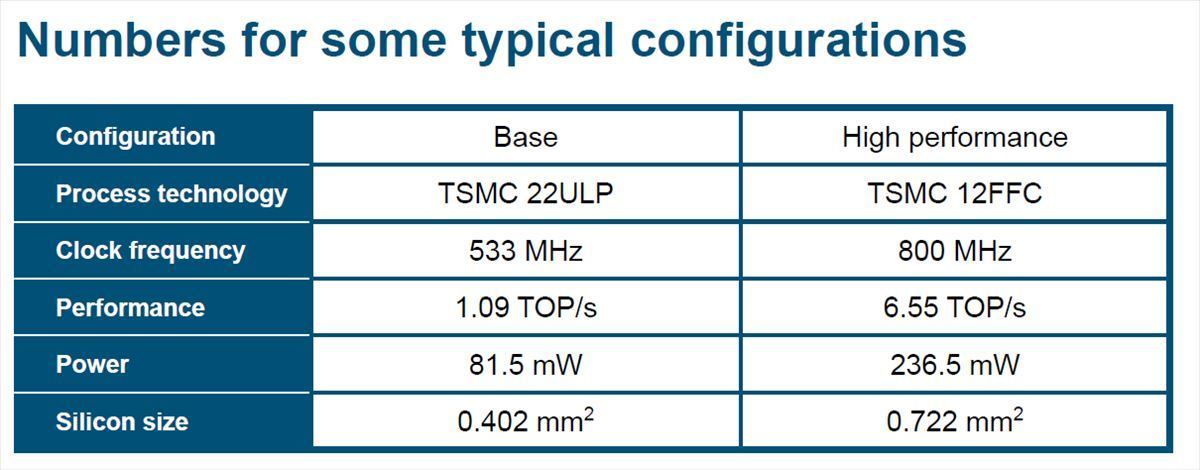

典型的な構成は、基本構成はTSMCの22ULPを使うASICで、クロックは533MHzで1.09TOPS、消費電力は81.5mWである。このASICのチップサイズは0.402mm2である。より高性能が必要な場合はTSMCの12nmプロセスである12FFC版が使える。このチップのクロックは800MHzで、演算性能は6.55TOPSで、消費電力は236.5mWである。このASICのチップサイズは0.722mm2である。

-

Efficieraの典型的な構成。基本構成ではTSMCの22ULPプロセスを使い、クロックは533MHzで、性能は1.09TOPS。高性能ではTSMCの12FFCプロセスを使い、クロックは800MHzで6.55TOPS

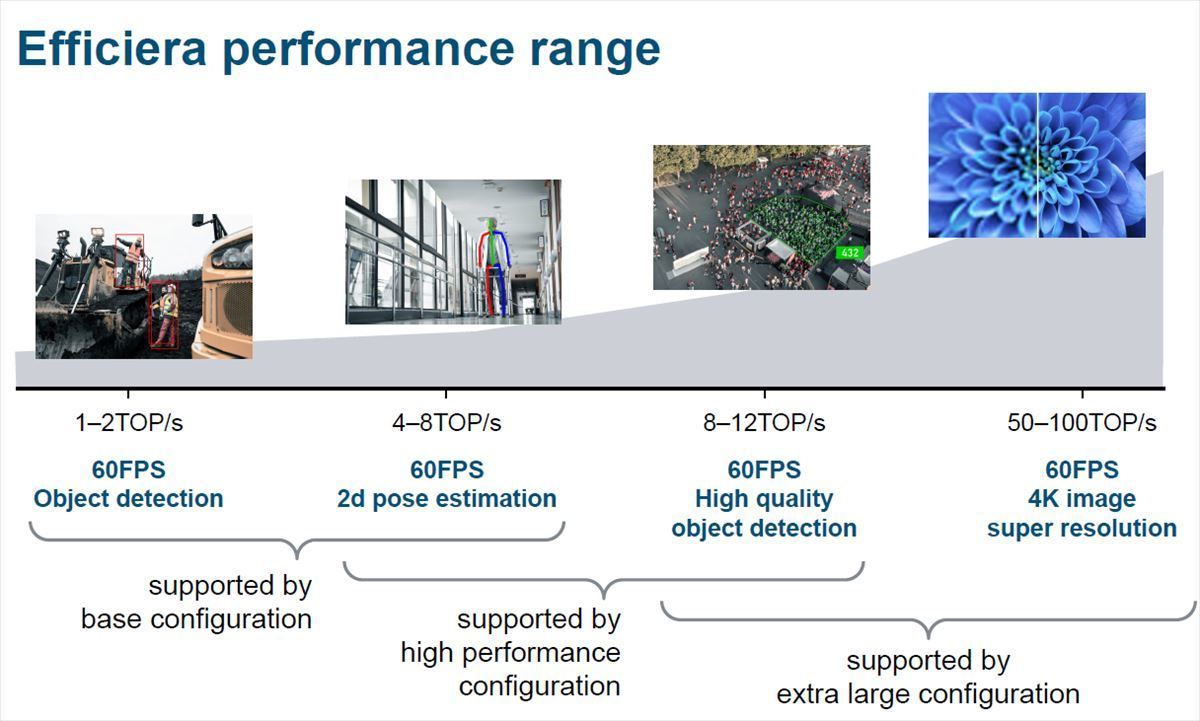

Efficieraでどの程度の処理ができるかを示すのが、次の図である。オブジェクト検出は1-2TOPSででき、姿勢推定は4-8TOPSでできるので、Efficieraの基本構成で手の届きそうな仕事である。一方、高品質なオブジェクト検出は複数のEfficiera IPを必要とする。

ベース構成では0.402mm2、高性能構成でも0.722mm2とチップは非常に小さく、価格的にも安く出来そうである。また、複数のEfficiera IPを載せたチップも造りやすい。

FPGA版はIntelのCyclone V SoCを使った場合、140MHzクロックで動作し1.1TOPSの性能が得られる。この性能があれば顔の検出や歩行者の検出などのよく用いられる機能を実現できる。

β版チップは2020年5月にリリース予定

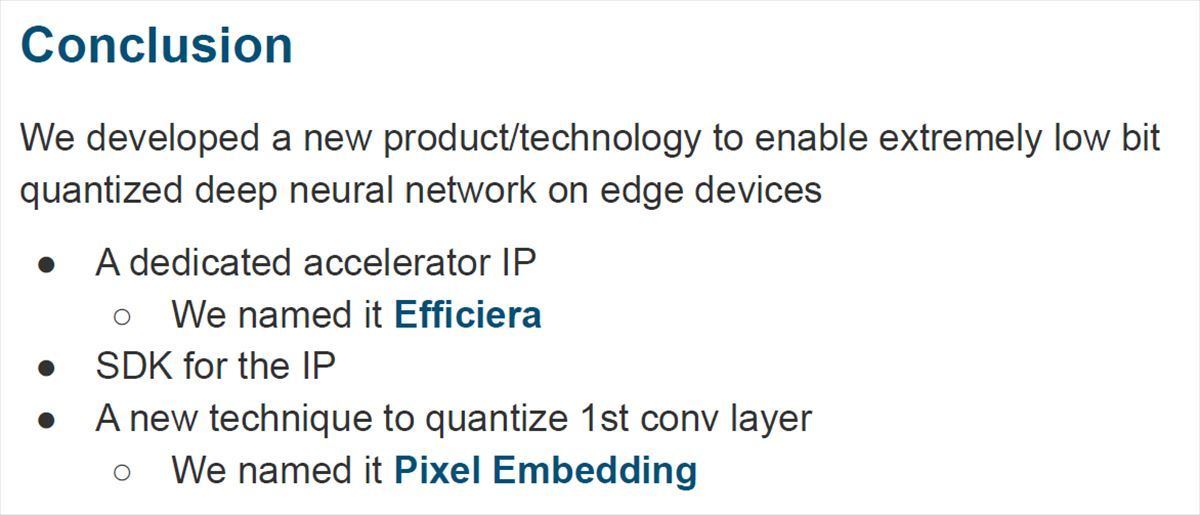

結論であるが、LeapMindは非常に少ないビット数での量子化を行うエッジデバイス用のDNN(Deep Neural Network)テクノロジと製品を開発した。このDNNアクセラレータはEfficieraと名付けられている。低ビット数のDNNはソフトウェアが重要で、このIP用のSDKを開発した。

LeapMindは、精度低下を抑えて、最初の畳み込み層をQuantizeする手法を開発し、Pixel Embeddingと名付けた。

現在はアルファ版のチップが動いているが、5月にベータ版チップをリリースする予定である。そして、製品版を2020年の秋にリリースする予定である。