Hot Chips 31でAMDはGPU「Navi」を発表した。Navi自体は5月ころから情報が出始め、7月7日に正式発売された。しかし、Hot Chips 31での発表は初めての学会発表であり、従来より詳しいマイクロアーキテクチャが発表された。

Naviは2012年に発表されたCGNアーキテクチャに替わるRDNAアーキテクチャの最初のGPUである。RDNAアーキテクチャの特徴はゲーミングにフォーカスしたアーキテクチャになっている点である。

NVIDIAはFermiアーキテクチャから、グラフィックス用に加えて科学技術用もカバーするアーキテクチャを採用し、AMDもそれに追随したが、最近では科学技術用とゲーミング用と、さらに機械学習用のすべての機能を1チップに入れるのは重くなり過ぎるという反省が出てきている。そのため、RDNAアーキテクチャでは科学技術用の機能を減らし、ゲーミング用にフォーカスしたアーキテクチャになっている。

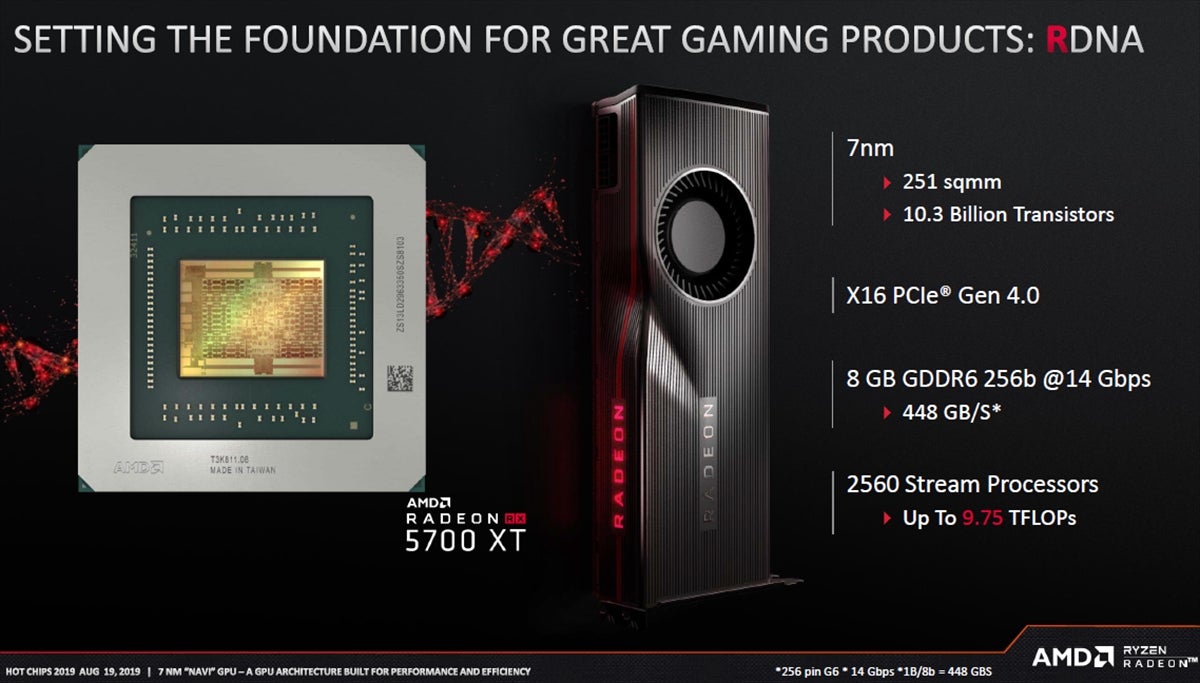

次の図の左側の図は「Radeon 5700 XT」のチップ(ただし、チップとパッケージ基板を接続するため、チップはFace Downでマウントされるので、本当はチップの配線などのパターンは見えない。これは合成写真である)で、右はGPU製品の外観の写真である。

Radeon 5700 XTは7nmプロセスで作られ、チップサイズは251mm2、集積するトランジスタ数は103億である。2560個のストリームプロセサを持ち、ピーク演算性能は9.75TFlopsに達する。8GBのGDDR6メモリを搭載しピークメモリバンド幅は448GB/sである。そして、CPUとの接続はPCIe 4.0をサポートしている。

-

RDNAアーキテクチャの最初のGPU製品のRadeon 5700 XT。7nmプロセスで製造され、251mm2のチップに2560個のストリームプロセサを集積する。ピーク演算性能は9.75TFlops。GDDR6メモリを使い、メモリバンド幅は448GB/s (出典:このレポートのすべての図は、Hot Chips 31でのAMDのMike Mantor氏の発表スライドのコピーである)

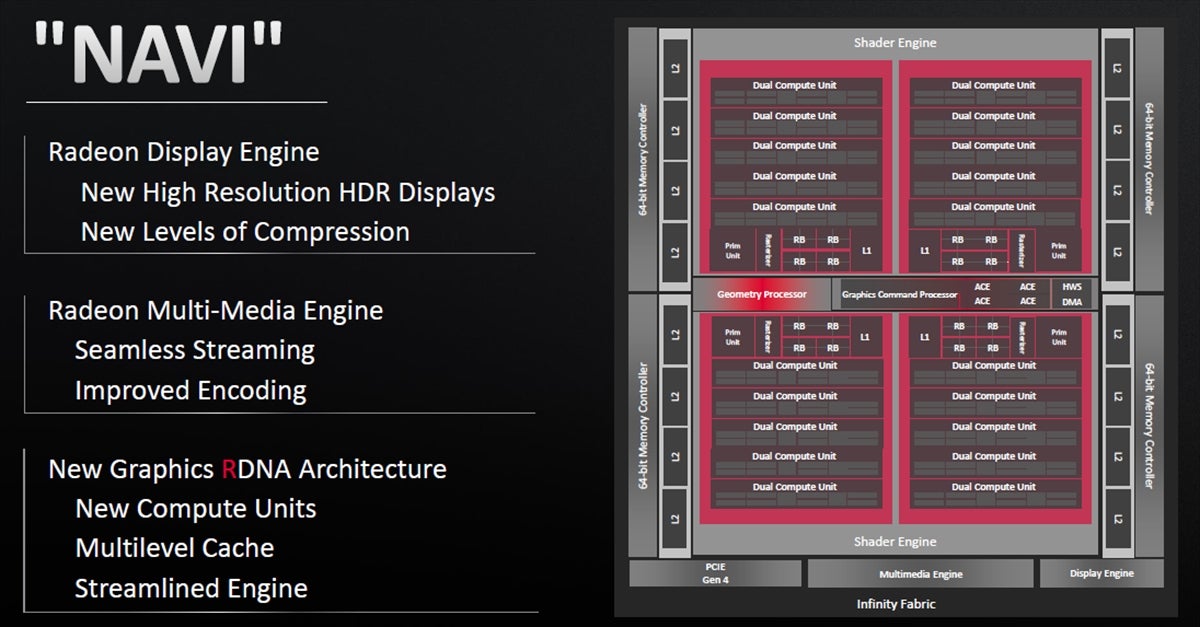

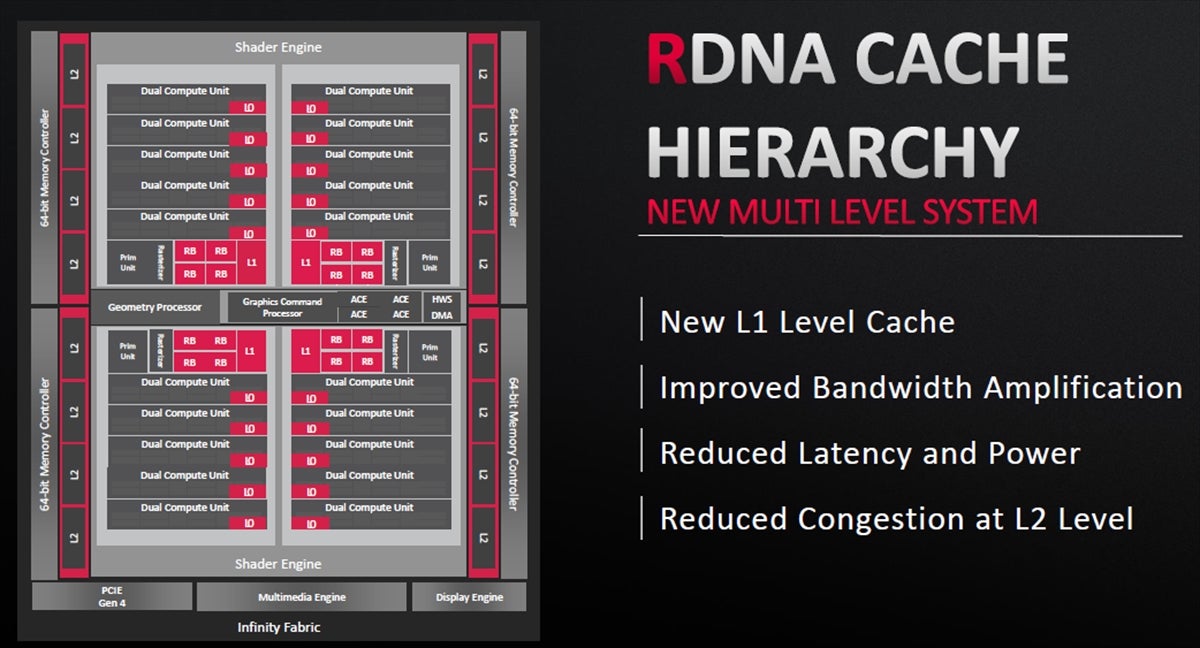

Naviは新アーキテクチャのGPUであり、新設計のディスプレイエンジンを持ち、マルチメディアエンジンも切れ目のないストリーミングが行なえるようになっている。そして、グラフィックスの部分は新開発のRDNAアーキテクチャとなっている。RDNAアーキテクチャではコンピュートユニットが新設計となり、L1キャッシュが追加されてマルチレベルのキャッシュとなった。計算エンジンも無駄を省きゲーミングにフォーカスしたものとなっている。

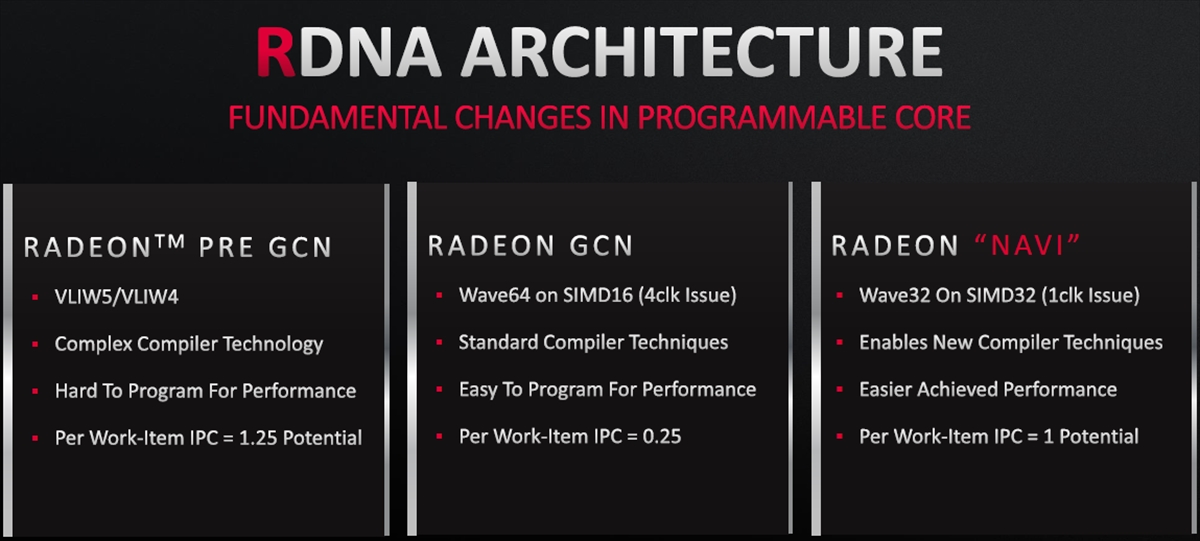

次の図はGCN以前のアーキテクチャとGCNアーキテクチャ、そして、新しいRDNAアーキテクチャの特徴を比べたものである。GCN以前のアーキテクチャはVLIW5/VLIW4という1命令に4~5演算を詰め込むアーキテクチャで、コンパイラでうまく演算を詰め込むのが難しかった。GCNアーキテクチャはSIMT型の命令で標準的なコンパイラが使え、コンパイラで効率の高いプログラムを作れるようになった。しかし、64スレッドのWave64を16SIMDの演算器で4サイクル掛けて処理しており、ゲーム用としては命令実行のレーテンシが長いのが欠点である。

これに対して、RDNAではWave32を32SIMDの演算器で1クロックで発行できるようになり、命令の実行レーテンシが改善された。また、1命令を1クロックで発行できるので、コンパイラによる新しい最適化もやり易くなった。

ただし、Waveが32スレッドと大きくなったため、多くのWaveを作り、細かい制御を行う科学技術計算には多少不向きとも言える。しかし、ゲーミングのグラフィックスであれば並列に実行するスレッドは大きいので問題にならない。また、Wave32は制御系も簡単になる方向であり、良いことずくめである。

-

GCN以前はVLIWに4、5命令を詰め込むアーキテクチャであり、プログラミングが難しかった。GCNでプログラミングは簡単になったが、Wave64をSIMD16で4サイクルで発行しており、命令発行に4サイクル掛かるのが難点である。NAVIではWave32をSIMD32で1サイクルで命令発行するので、命令発行のオーバヘッドが小さくなった

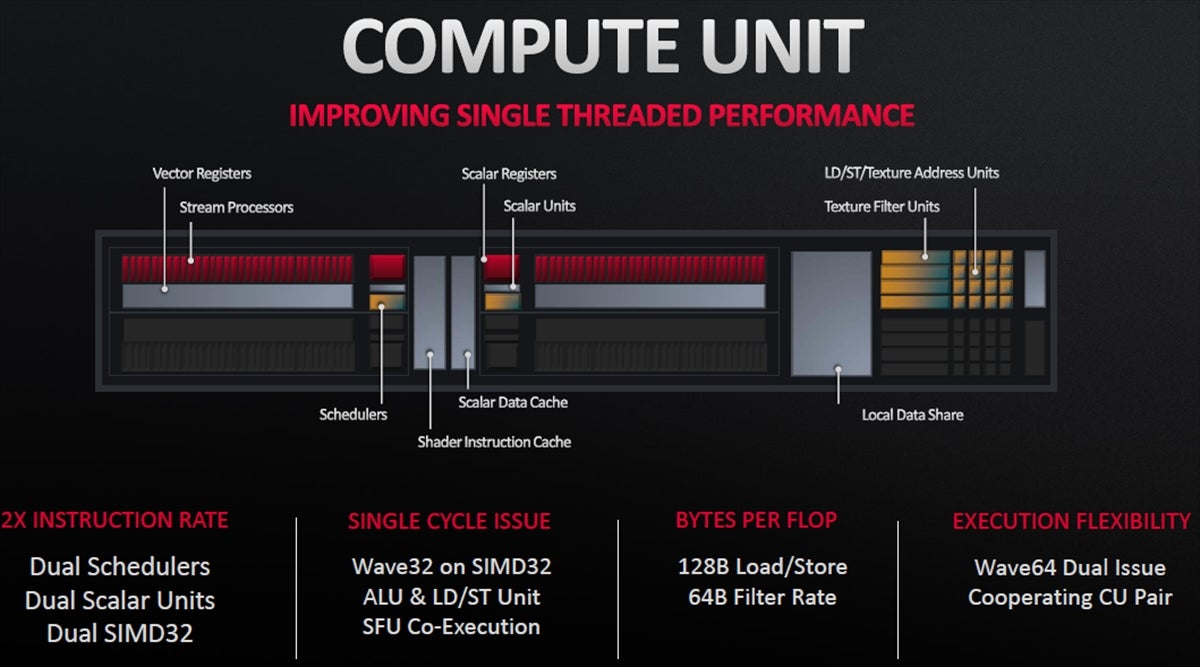

コンピュートユニット(CU)には32個のストリームプロセサとベクタレジスタがペアになったベクタ演算ユニットが4個入っている。そして、スケジューラとスカラユニットがそれぞれ2個ずつあり、GCNに比べると命令発行レートは2倍となっている。図の右端にテクスチャフィルタユニットとロード/ストアユニットがあり、RDNAのCUは、1サイクルに64Bのフィルタリング、1サイクルに128Bのロード/ストアを実行できる。

-

Compute Unitには32SIMDのベクタエンジンが4個あり、Wave32命令などは1サイクルで発行できる。Load/Storeは128B/Cycle、テクスチャフィルタリングは64B/サイクル実行できる

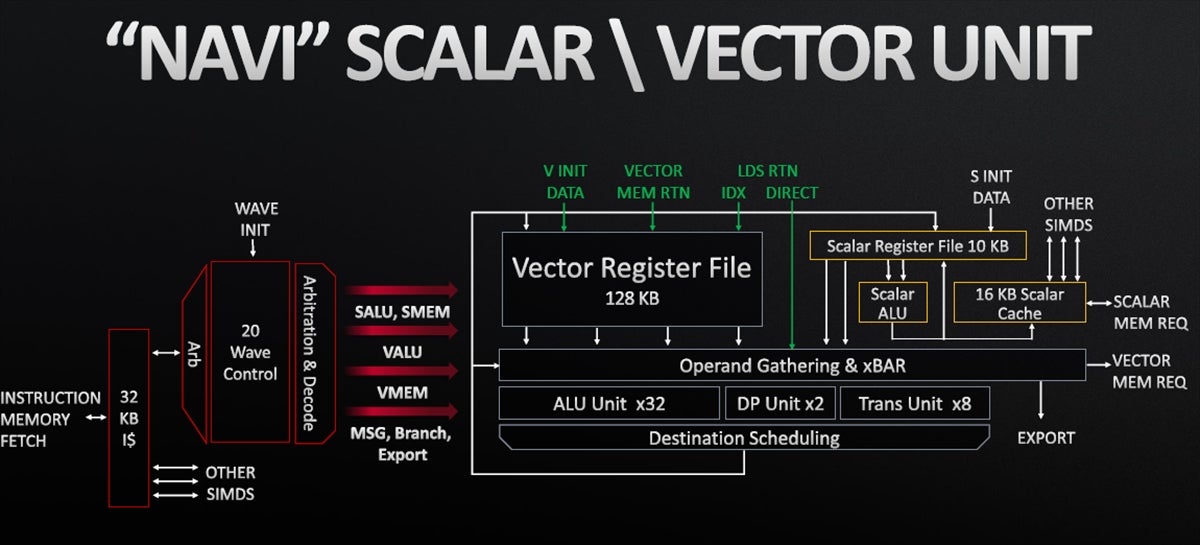

Naviのスカラとベクタユニットのブロックダイヤグラムは次の図のようになっている。ベクタのレジスタファイルは128KBで、演算器の数は32個である。なお、倍精度浮動小数点演算器は2個しかないので、単精度の1/16の性能しか出ない。スカラのレジスタファイルは10KBで、16KBのスカラキャッシュが付いている。

実行中のスレッドの情報を保持するWave Controlは20エントリであり、多いとは言えないがゲーム用としては十分であろう。

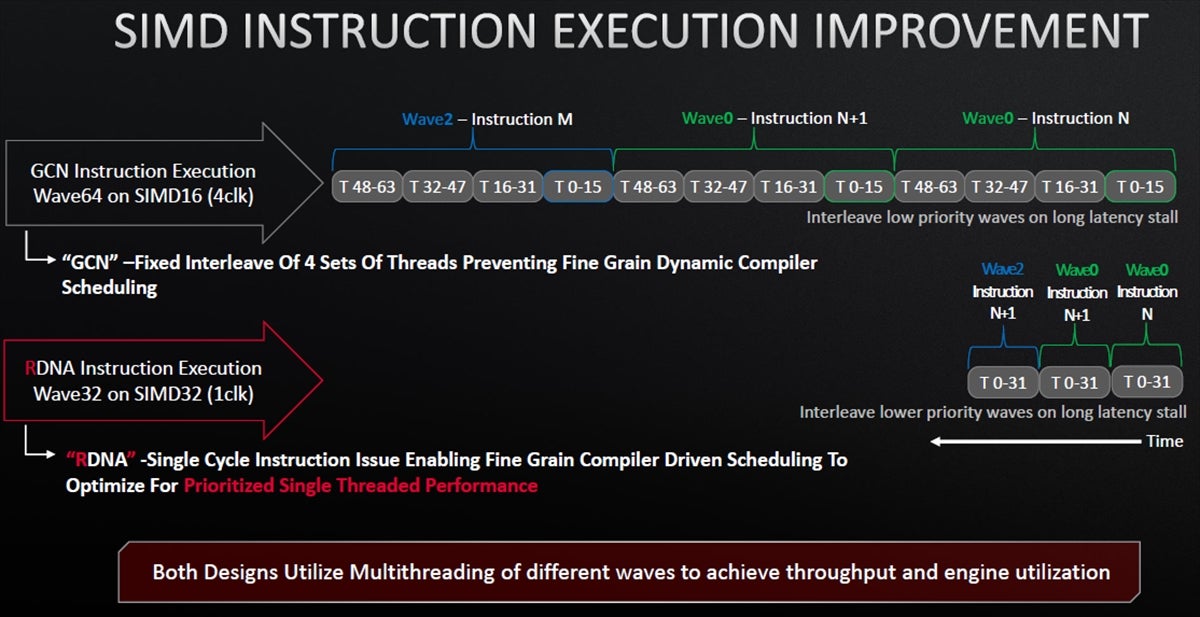

次の図はGCNで4サイクル掛けてWave64を発行する場合(上)とRDNAでWave32を1サイクルで発行する場合(下)の命令の発行の様子を示している。GCNでは4サイクルでWave0の命令Nを発行し、それに続いて4サイクルでWave0の命令N+1を発行し、その次はWave2の命令Mを発行している。

下の図は1サイクルでWave32を処理できるので、最初のサイクルでWave0の命令N 、次のサイクルでWave0の命令N+1を処理し、その次のサイクルにはWave2の命令N+1(命令Mと書いてくれた方が分かりやすかった)を発行している。

なお、GCNアーキテクチャでもRDNAアーキテクチャでも演算器の数が同じであれば、演算スループットは同じであるが、GCNでは1つの命令を16個の演算器に供給するのに対して、RDNAでは1つの命令を32個の演算器に供給するので、命令発行に2倍の時間がかかるという違いがある。

上の図は64スレッドを実行するのに対して、下の図は32スレッド実行であるので、もし64スレッドを実行するなら、2倍の6サイクル必要になるが、それでもGCNの12サイクルと比べると半分のサイクルで命令を発行できる。

そして、RDNAでは各命令の発行が1サイクルででき、マルチサイクルの命令が無いので、コンパイラによる細粒度の最適化もやり易い。

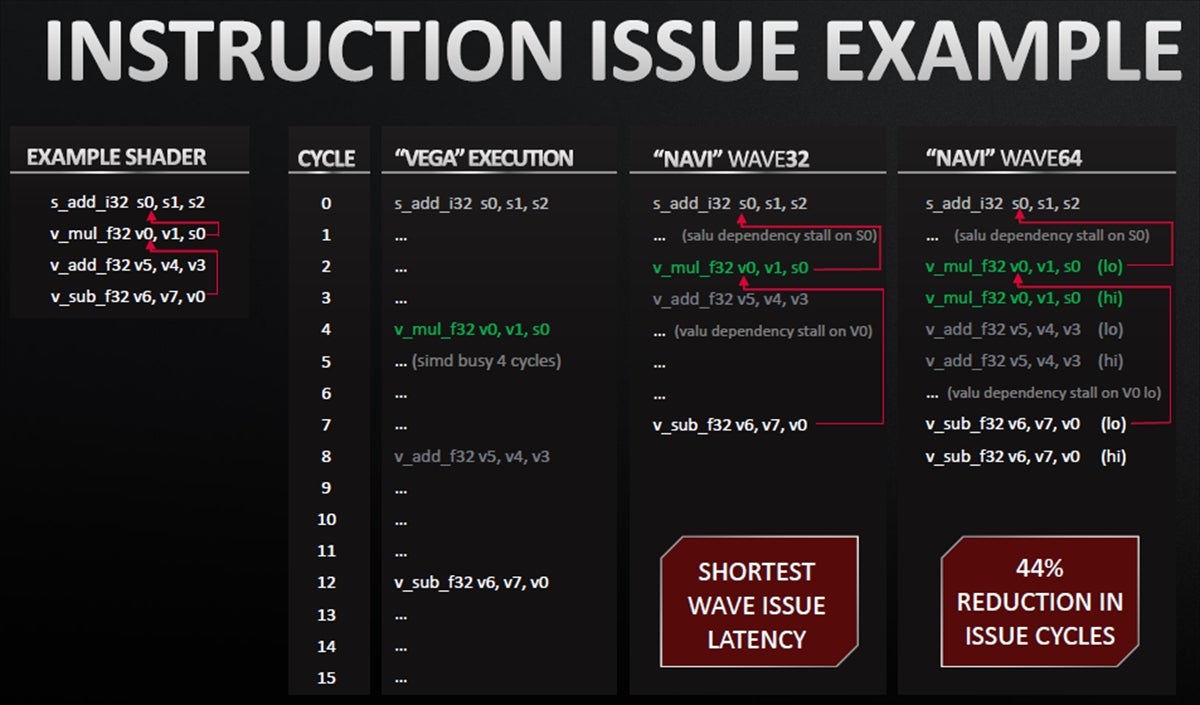

次の図はシェーダーの命令列をGCNのVega GPUで実行した場合とNAVI GPUのWave32モードで実行した場合とNAVI GPUでWave64モードで実行した場合の各サイクルでの実行の様子を比較したものである。

Vegaの場合は4サイクルごとに1命令ずつ発行されていく。NAVIのWave32モードの場合は演算器のレーテンシによる待ちが入る場合があるので4サイクルでは実行できないが、この例では8サイクルで発行できる。そして、同じ命令をWave64モードで実行しても9サイクルで4命令のシーケンスの発行が終わる。これはVegaの場合と比べると44%短い命令発行サイクルで済むことになる。

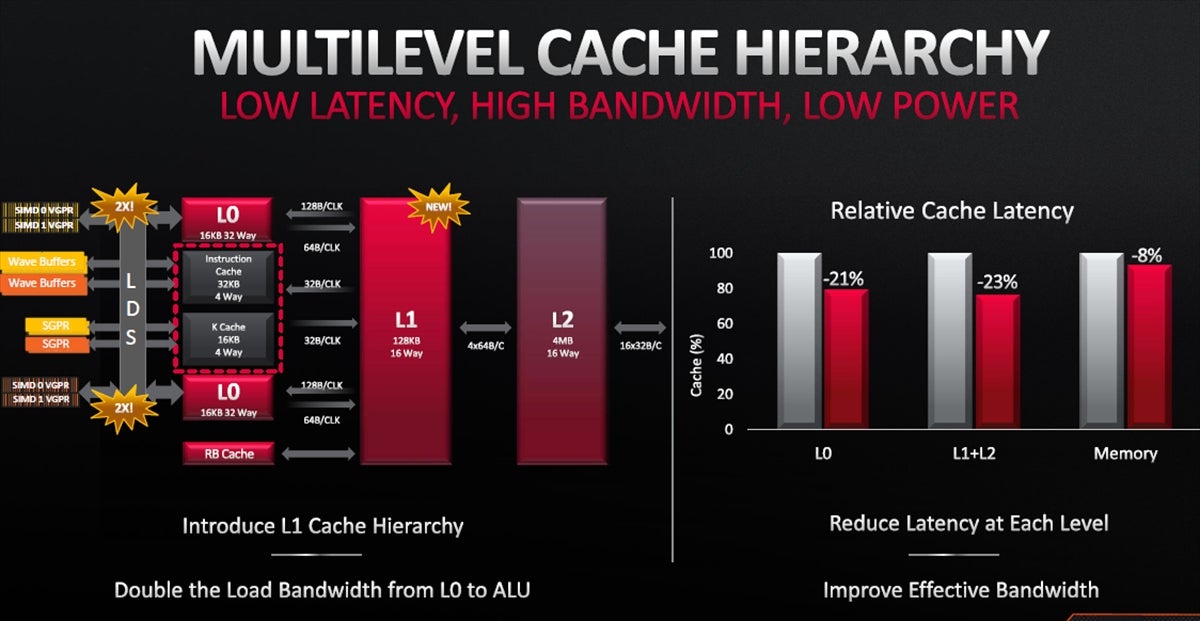

そして、RDNAでは新たにL1レベルのキャッシュが追加され、L2キャッシュのアクセス頻度も低くなり、結果としてレーテンシや消費電力が改善されている。

次の図はキャッシュの階層を示すもので、RDNAアーキテクチャでは新たにL1キャッシュの階層が設けられ、Navi 10 GPUでは128KBの16wayのキャッシュとなっている。そして、L2キャッシュは4MB 16wayであり、512B/CycleのバスでGDDR6メモリに繋がっている。また、NaviではL0キャッシュとALUの間のバンド幅がGCNの2倍に増強されている。

結果としてL0キャッシュのレーテンシは21%短縮され、L1+L2キャッシュのレーテンシは23%短縮、メモリレーテンシは8%の短縮となっている。

-

RDNAアーキテクチャではL0キャッシュとALUの間のバンド幅が2倍となり、L1キャッシュが新設された。この結果、L0キャッシュのレーテンシは21%減少し、L1+L2キャッシュのレーテンシは23%減少した。また、メモリのレーテンシも8%減少した

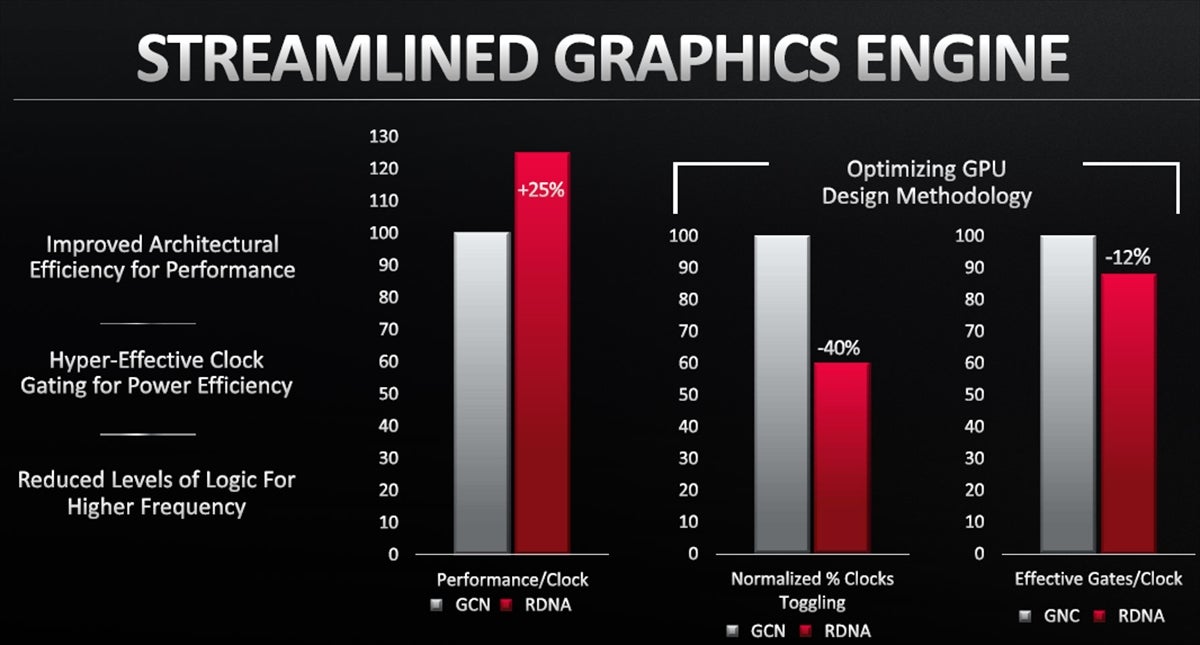

グラフィックスエンジンのクロックあたりの性能は、RDNAアーキテクチャで25%改善され、設計手法の改善でクロックがゲートされていないで動作している回路の割合は40%減り、クロックあたりで動作するゲートの割合も12%減り、消費電力の低減に貢献している。

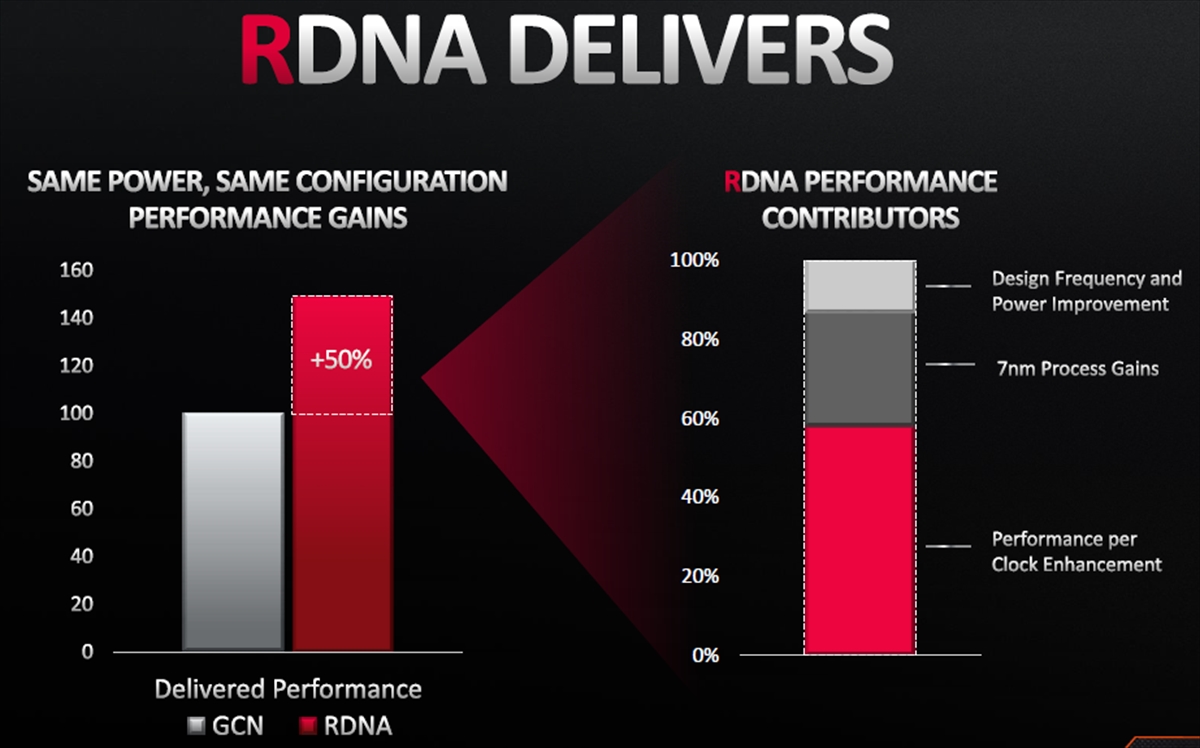

次の図の左のグラフは、同一電力、同一構成での性能の比較で、RDNAアーキテクチャにより、GCNに対して50%性能が向上したことを示す。右のグラフは、この50%の改善の内訳を示すグラフで、60%は性能/クロックの改善によるものであり、25%程度が7nmプロセスによる改善、残りはクロック周波数の向上や電力の低減によるものである。ただし、アーキテクチャの改善による効果は、ゲーミング用にフォーカスした効果も含まれている。

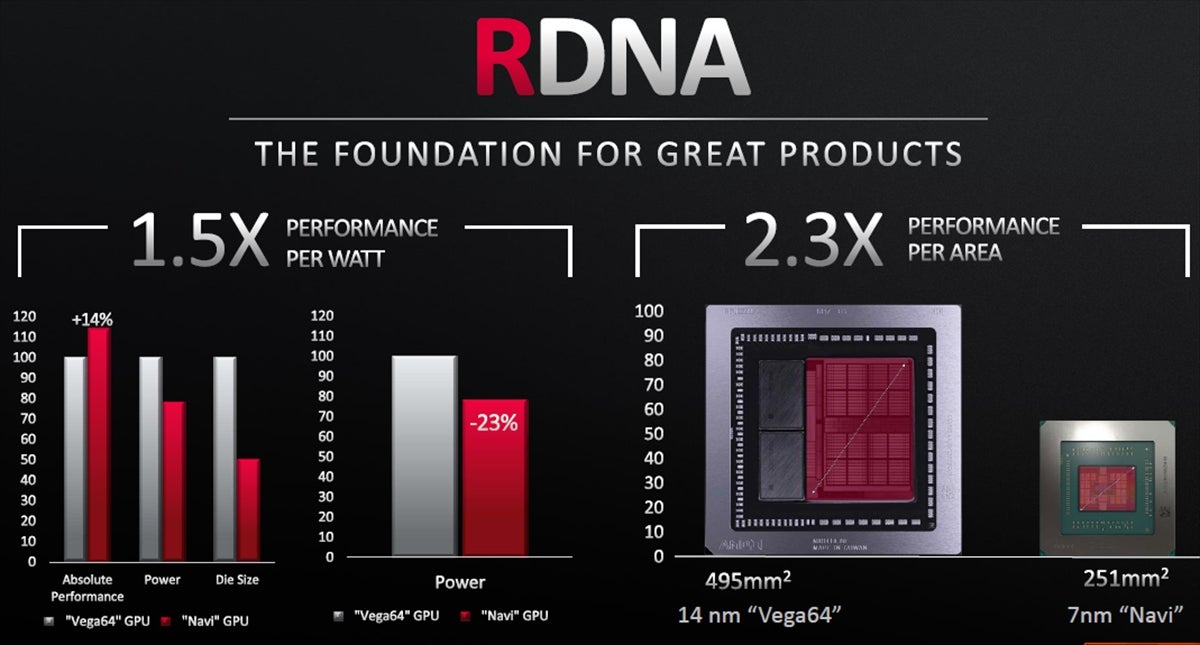

まとめると、RDNAはAMD GPUの次世代の基礎であり、GCNと比較して性能/電力は1.5倍、チップ面積あたりの性能は2.3倍になっている。