英Armはパシフィコ横浜で11月14日~16日にかけて開催されている「ET 2018」にあわせ、11月15日に記者説明会を開催、Cortex-A5を対象としたDesignStartについての説明を行った(Photo01)。

-

説明を行ったPhil Burr氏。Photo01:筆者はつい最近、別の場所(XDF)でも同氏にお会いしている)

説明会はまずDesignStartそのもの、ついでDesignStart FPGAの説明が行われたが、この部分は先日のXDFにおける説明会の内容と重複するので割愛させていただき、DesignStart Cortex-A5についての話を中心に深堀りしたい。

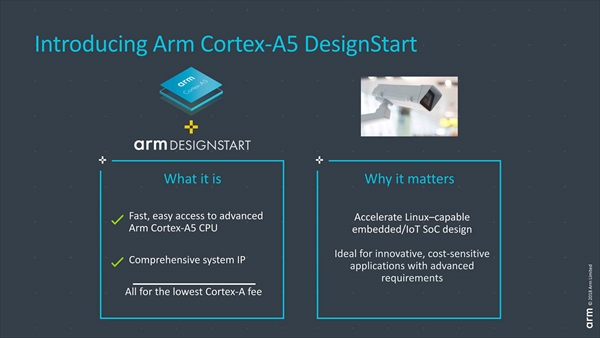

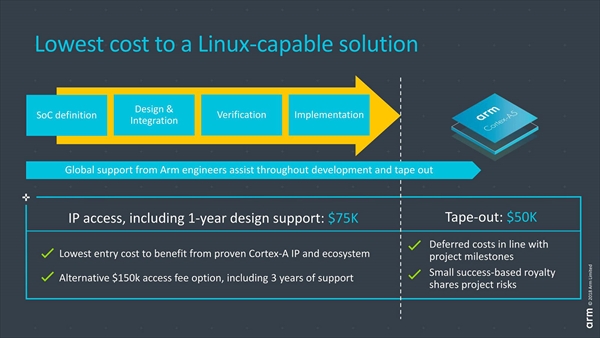

DesignStartの対象をCortex-A5まで広げる、という話は10月22日に発表されたが、ターゲットとするのは、Embedded Linuxを必要とするような、より複雑な機器向けのSoCとなる(Photo02)。

Cortex-A5はどのようなプロセッサコアなのか?

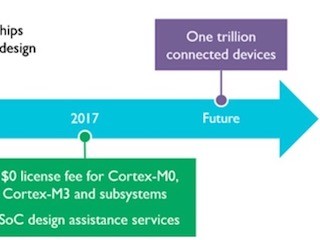

Armは2009年にCortex-A5を発表以来、すでに20億個以上の製品が出荷されているとする(Photo03)。

-

Photo03:初期にはモバイル向けSoC(Snapdragon S1/S4 PlayとかSpreadtrum SC8810とか)での採用例が多かったが、2010年台に入ってからはAtmelのSAMA5シリーズやFreescale(現NXP)のVybridなど、Embedded Controller向けのニーズが増えてきた

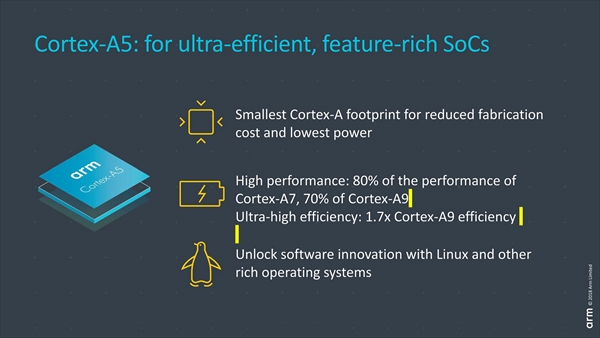

内部構造はSingle Issue/Single Pipelineなのでそれほど高性能という訳ではない(1.57 DMIPS/MHz)が、それでも組み込み向けなどの用途では十分だし、Cortex-M系に比べればずっと性能は高い(Photo04)。

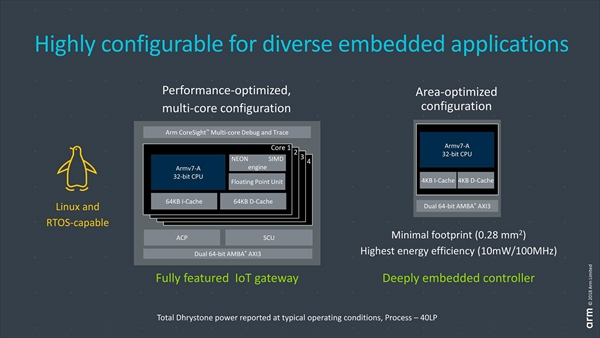

そのCortex-A5だが、当初から4コア構成をサポートしており(Photo05)、さまざまな構成を選択できるとする(Photo06)。

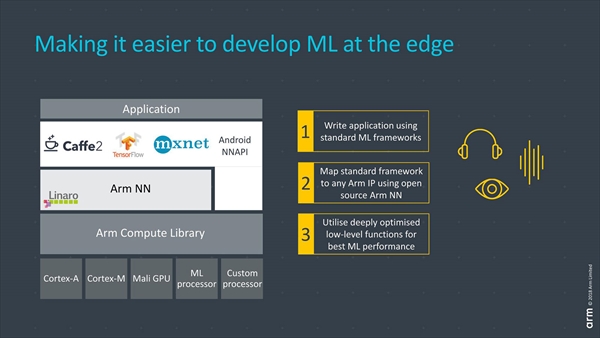

また昨今Armはマシンラーニング(ML)向けにも力を入れている訳だが、例えばCortex-A5をコントローラとし、その下にカスタムアクセラレータをつなぐといった構成を取りやすい事もアピールした(Photo07)。

-

Photo07:ポイントはCortex-A5を利用することで、Arm Compute LibraryやArm NNというソフトウェア資産を利用できる様になる、という事だ。ちなみにCortex-A5ではNEONを利用できるため、これをつかってMLの実行も出来なくはないが、むしろArm NNに基づく形でアプリケーションを記述すれば、それはCortex-A5だけでなく、その下にぶら下がるアクセラレータで(アプリケーションの変更なく)そのまま利用できる点が重要との事だ

Cortex-A5に向けたDesignStartの特徴とは?

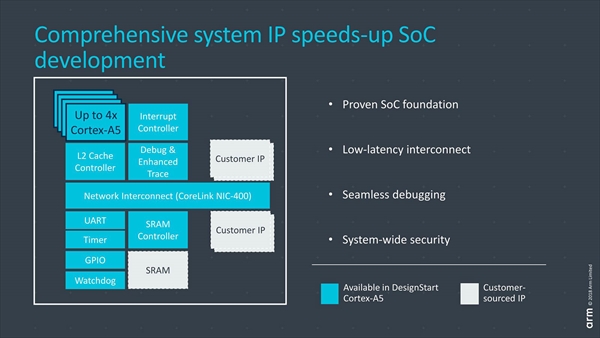

ということで話をDesignStartに戻す。Cortex-A5に向けたDesignStartでは、最大4つのCPUコアに加え、Interconnect(CoreLink NIC-400)とInterrupt Controller、L2、Debug&Traceなどに加え、必要な周辺回路までがすべて一括して提供される(Photo08)。

そのため、あとは顧客独自のIPを組み合わせれば、ASICが作れるという仕組みとなっている。さて、そのASIC作成だが、DesignStartでは、Photo08に示したすべてのIPのアクセス権(とライセンス)、それと1年間のサポート付きを7万5000ドル、サポートを3年に増やしたものを15万ドルで提供したうえで、デザインが完了してTapeoutした段階でさらに5万ドルの追加費用、という形になっている。

5万ドルの追加費用と書くとイメージが悪いが、実のところ本来であれば12万5000ドルの初期費用となるところを2つに分割した、という方が実情に近い。これは要するにDesign InしたもののTape outに漕ぎつけなかったというケースを考慮したものだ。

一括だと12万5000ドルが無駄になるが、分割にすることで5万ドルの節約になる、こうした形態にすることで、特に小さなスタートアップ企業におけるリスクを軽減しよう、という試みだとBurr氏は説明した。

想定はあくまでSoC/ASICへの適用

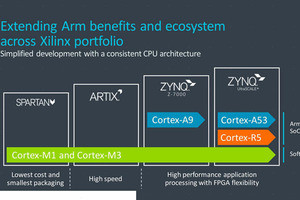

ちなみにCortex-A5については、FPGAへのポーティングは考えていないとの事。「技術的には不可能ではないと思う」としながらも、(Cortex-Mはともかく)Cortex-Aを使うようなプロジェクトでは、FPGAはプロトタイピングには利用されても、最終製品をFPGAで入れるケースはまだ少ないと思う、との話だった。

実のところ、もしFPGAで最終製品まで持ってゆくのであれば、XilinxのZynqとかIntelのCyclone V/Arria Vなどの様に、Cortex-A9をハードコアで統合した製品を使う方が効率が良い、というあたりもあるのだろうとは思う。

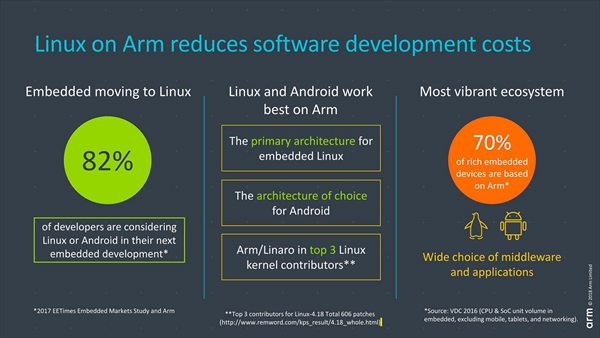

ちなみに(Cortex-Mではなく)Cortex-A5を選ぶ理由としてBurr氏が示したのは、Embedded SystemがどんどんLinuxやAndroidベースにシフトしており、またArm自身もLinaroと組んでKernel Contributionを積極的に行っており、すでにArm+Linux/Androidという組み込みのシステムが主流になりつつある事を踏まえ、それをCustome SoCで実現するための最小構成がCortex-A5だ、という事であった(Photo10)。

-

Photo10:とはいえ、Linux DistributionはともかくAndroidについては、これを例えばArmがPre Buildして提供するといった考えはないそうで、そうしたものはパートナーからの提供になるという話であった

Burr氏のメッセージは「ASICと言えばコストが高いと思うかもしれないが、最先端はともかくとして180nm~90nmといったあたりでは初期コストは非常に安いしリスクも少ない。Cortex-A5は幅広いプロセスノードに対応しており、最先端のプロセスでなくても製品差別化要因はあるし、そうしたところにCortex-A5を利用することで、特にソフトウェア側の開発が容易になる」であった。