ベルギーimecとCadence Design Systemsは月28日(米国時間)、半導体業界初となる3nmテストチップのテープアウトを完了したと発表した。

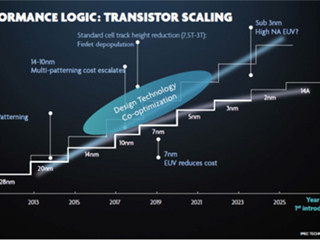

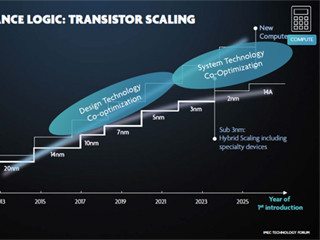

両社の共同開発プロジェクトは、Cadenceの一連のEDAツール(Innovus Implementation SystemおよびGenus Synthesis Solution)を使用して、EUVおよび液浸ArFリソグラフィを併用することを前提に開発され、64bit CPUを用いて3nmのカスタムスタンダードセルライブラリとTRIMメタルフローを使用したほか、配線ピッチ21nmを実現したという。

両社は今回の協業により、次世代のデザイン革新に向けた3nmインプリメンテーションフローを完全に検証することができたとしている。

なお、imecの半導体技術およびシステム開発担当EVPのAn Steegan氏は、今回の成果について、「回路パターンのサイズが3nmまで縮小されると、配線のバラつきがますます大きくなる。今回のテストチップの取り組みを通じて、配線のバラつきを測定して改善することが可能となることから、3nmプロセスの実現性を検証することができた」とコメントしている。