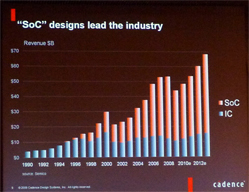

半導体設計の大半を占めるSoC

ここでTan氏は話題を半導体設計に転じた。半導体設計をIC設計とSoC(System on a chip)設計に分けると、設計の大半はSoC設計となっている。SoC設計は、大規模な回路と膨大な数のトランジスタを集積したチップの設計である。

設計作業は膨大なものとなり、何らかの工夫なしでは設計期間が大きく延びてしまう。ケイデンスは半導体ベンダと協力してSoC設計の効率向上に取り組んでおり、日本市場における例としてTan氏はルネサス テクノロジとの協同作業を挙げていた。協同作業の結果、設計変更に伴う作業時間が従来の1/5に短くなったとしている。

現在のSoCは、デジタル回路だけで構成されている訳ではない。アナログ回路を含むのが普通である。このためSoC設計はアナログ・デジタル混在回路の設計(ミクスド・シグナル設計)となっている。大規模なミクスド・シグナル設計を効率良く進めるには、システム・レベルで設計し、設計内容を検証する環境が欠かせない。ケイデンスは従来よりも設計の抽象度を高めたトランザクション・レベル・モデリング(TLM)で設計と検証を実行することで、大規模なSoCの開発期間を短く抑え込もうとしている。ここまででTan氏は講演を終えた。

設計と検証で生産性のギャップが増大

続いて米国本社で戦略マーケティング担当コーポレート・バイス・プレジデントを務めるSteve Glaser氏が登壇し、基調講演の後半を引き受けた。講演タイトルは「Lowering the Cost of SoC Design」である。

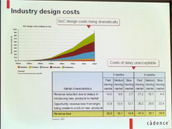

Glaser氏は初めに、半導体製造技術が微細化するごとに、SoCの設計コストが急速に上昇していくことを示した。また設計の遅れがもたらす損害額(市場機会を逃すことによる見込み売上額の減少)が、許容し難い水準に上がってきていると述べた。

こういった事態を防ぐには今後、設計の生産性と検証の生産性を大きく向上させなければならない。しかし生産性の向上は容易ではない。2008年の生産性を「1」とすると、検証の生産性は2015年に「6」に高まるのに対し、設計の生産性は2015年に「4」に留まり、設計と検証で生産性のギャップが増大するという。

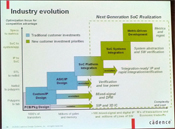

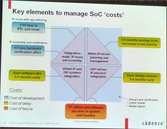

設計の生産性を高めるには、回路コア(IP)の再利用はもちろんのこと、回路コアをSoCに組み合わせてから最適化したり調整したりするのではなく、初めから組み合わせることを前提にした調整済みの回路コア(Integration-ready IP)を用意することが望ましい。こうすることで、数多くの回路コアを組み合わせて設計を検証する作業の負担を軽減する。現在の回路コアでは、組み合わせてからの調整と検証に時間がかかり過ぎる。

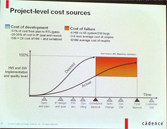

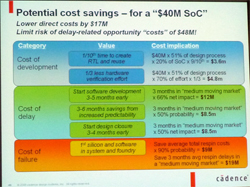

Glaser氏は最後に、4,000万ドルのSoC開発プロジェクトを例に、ケイデンスの提供する設計ソリューションによってコストをどの程度削減できるかを示した。結果としては、直接コストを1,700万ドルにまで削減できる可能性があるという。また設計遅延と設計変更の発生に伴う損害4,800万ドルの発生を避けられるとした。