NVIDIAの「Tesla V100」Volta GPUは、ディープラーニングに大きく舵を切った。科学技術計算に舵を切ったFermi GPUの時と似たNVIDIAのビジネス戦略の変更であると考えられる。

NVIDIAのGPUチップは、「GP100」のようにGとアーキテクチャ名の頭文字、Pascalの場合はPをつけ、それに100のようなチップの番号を付ける。なお、伝統的に最高性能の科学技術計算用のチップには100番が付けられている。しかし、今回はGV100という名称はあまり使わず、Tesla V100ということが多い。Teslaは科学技術計算用のGPUのシリーズ名であるので、科学技術計算用GPUのV100チップと呼ぶことに変わったようである。

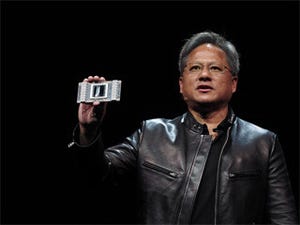

そういえば、NVIDIAの創立者兼CEOの名前が、今回からJensen Huangに変わった。アメリカ人の発音はジェンセンに変わると思うが、日本では、これまでのなじみがあるジェンスンを使い続けるとのことである。この「ス」と「セ」の争いはどちらに軍配が上がるのであろうか。

トランジスタ密度とトランジスタ数の謎

閑話休題で、Tesla V100に話を戻すと、このチップはTSMCの12nm FFNプロセスで作られている。FFNはNVIDIA向けのFinFETプロセスという意味であろう。従来から、配線本数の多いGPUのために高密度の配線を多く使えるようにプロセスのカスタム化を行っていたので、今回も、12nmトランジスタの基本設計ルールは標準プロセスと同じであるが、このような一部カスタム化を行ったプロセスを使っていると考えられる。

チップサイズは815mm2と発表された。NVIDIAは、このサイズは製造限界ギリギリであるという。集積されているトランジスタ数は21.1Bと発表された。このチップサイズ、トランジスタ数は知る限りではこれまで最大で、GP100チップの610mm2を33.6%上回っている。

微細加工では業界標準であるオランダASMLのTwin Scan T1950iスキャナの露光面積はX方向最大26mm、Y方向最大33mmとなっている。これはチップ面積では856mm2である。X、Yのサイズを露光装置の最大値に合わせて設計すれば、もう少し大きくできるかもしれないが、V100チップの815mm2は製造限界ギリギリというのは正しく、現在の製造装置では、V100よりも大きいチップは作れない。その意味ではNVIDIAのV100は集積度の限界を追求したチップである。

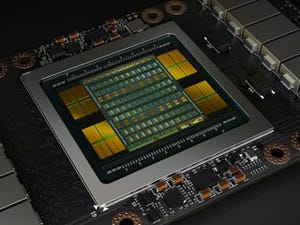

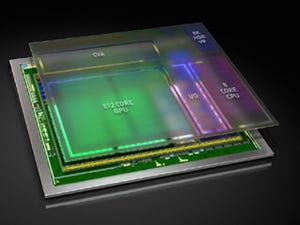

次の図は「SMX2」というタイプのデータセンタ用パッケージのV100 GPUである。メザニンボードは写真と思われるが、中央の枠の中に入っているGPUの部分は、イメージ図である。本物はGPUも4個のHBM2チップもトランジスタがある部分は下側で、このアングルで見えるのは、チップの平らな背中である。ということで、せいぜいパートナンバーなどがレーザマーキングで刻印されている程度で、この図のようにLSIのパターンは見えない。

|

|

NVIDIAのSMX2タイプのTesla V100 GPU (出典:本連載コラムの図はNVIDIAのInside Volta: The World's Most Advanced Data Center GPUに掲載されたものである) |

V100 GPUは最大のチップサイズで21.1Bトランジスタを集積しているのであるが、そのトランジスタ数とトランジスタ密度には謎がある。16nmプロセスのP100から12nmプロセスになり、さらにチップ面積が33.6%増えたのであるから、単純に計算すると、トランジスタ数は2.375倍に増えても良い。しかし、実際にはP100 GPUの15.3Bから21.1Bと1.38倍にしかなっていない。トランジスタ密度を計算すると、V100は25.9MTr/mm2、P100は25.1MTr/mm2であるから、16nmから12nmにシュリンクしてもトランジスタ密度は3%程度しか改善されていない。

もう1つの不思議は、トランジスタ数である。V100の21.1Bトランジスタは、P100からわずか38%の増加である。一番多くのトランジスタを使っているL2キャッシュは4MBから6MBと50%増加、FP32とFP64演算器はこれも50%増加で、今回はP100には無かったINT32演算器とTensorコアが新設されている。また、SMあたりのレジスタファイルは256KBで容量は増えていないが、チップレベルでは56SMから80SMに増えているので、10/7(=1.43)倍で、この部分もチップ全体の1.38倍よりも多くのトランジスタが必要なはずである。

トランジスタ数の増加がなぜ、38%で済んでいるのであろうか?

(次回は5月22日に掲載します)