「Versal」の第3弾シリーズが登場

Xilinxは3月10日(米国時間)、同社の次世代製品であるACAP(Adaptive Compute Acceleration Platform)「Versal」の第3弾製品シリーズとなる「Versal Premium」を発表した。この発表に先立ち電話会議の形でこの同製品の詳細の説明が行われたので、ご紹介したい。

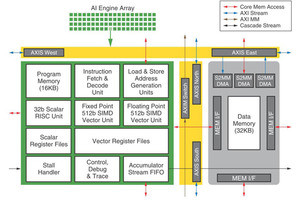

Versalシリーズ全体の概要は以前の記事でご紹介した通りで、FPGA FabricだけでなくS/W Programmable Engine(同社はこれをAI Coreという名称で説明している)やさらに高速化したI/Oを搭載、全体をNoC(Network on Chip)でつなぐという構成にした製品である。

2018年のXDFではこのVersalが6シリーズ用意されているとしており、AI処理向けの「Versal AI Core」と汎用の「Versal Prime」がまず発表になった形だが、今回追加されたVersal PremiumはVersal Primeの上位にあたる位置づけの製品である(Photo01)。

Versal Primeの内部構造はPhoto02のような具合であったが、Versal Premium(Photo03)はI/Oに機能的な強化が行われた。

-

Photo02:元々のVersal Prime

-

Photo03:Versal PrimeはPCIe Gen4どまりでSerDesは32Gと58Gのみ。またEthernetやInterlaken CoreもCrypto Enigineも搭載されていない

具体的には、

- PCIe Gen5に対応。またCCIXに加えてCXLへの対応を実装

- 112GbpsのSerDesを搭載

- 600GのEthenet Core/Interlaken Coreと、400GのCrypto Engineを搭載

といった点が異なる。

Versal Premiumのターゲットはネットワーク分野

明確にネットワーク向け処理に向けた製品である。実際Xilinx自身、16nmプロセス世代のFPGAと比較して、ことネットワーク向けで言えば22倍ものロジック密度が実現できるとしている(Photo04)。

どうしてこれが可能になったかと言えば、強化されたI/OがすべてハードウェアIPの形で搭載されており、FPGA Fabricを消費しないためである(Photo05)。

-

Photo05:ここには例として挙がっていないが、確かInterLakenも結構なLUTを消費したと記憶しており、こうしたものをハードIPで持っているからFPGA Fabricを使わずに実現でき、しかもFPGA Fabricを使うよりも当然低消費電力で実現できるから効率も良い

Xilinxでは、Versal Premiumを使う事で、基地局やバックエンドの機能を効率よく実装することができ、より効率の良いソリューションが提供できるとしている(Photo06)。

-

Photo06:赤の部分が製品差別化要因で、ここはFPGA Fabric(とDSP)を使って実装する。その他の部分はある意味共通化されており差別化要因とならないので、ここはハードIPで実装することで効率を上げる、という形

また従来の58G PHYに加えて112GのPAM4 PHYを搭載したことで、今後登場する800G Ethernetにも対応可能としている(Photo07)。

加えて、Versal Premiumでは600GのEthernetおよびInterlaken Coreを搭載している。特にハイエンドのVP1802の場合、600G Ethernet MAC×7、600G Interlaken×3、400G Crypto Engine×4という重装備で、アクセスラインのみならずメトロやコアネットワークであっても十分対応できるとする(Photo08)。

そのため、ここでの差別化要因はFPGA FabricとDSPを使ってどのような事が出来るかという話になってくる。こうした用途で昨今はAIを利用するケースが少なくない(Photo09)。