Sandra Platinum その1(グラフ53~73)

SiSoftware

http://www.sisoftware.co.uk/

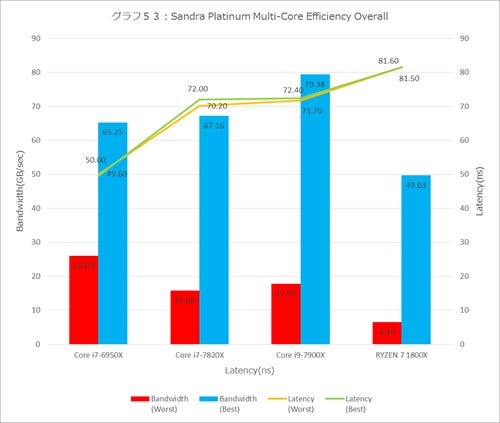

さて、次はMulti-Core Efficiencyである。まずグラフ53はOverallである。これはコア間でさまざまなサイズの通信を行ったときのLatencyとBandwidthをそれぞれ測定して集計したものである。Bandwidth/LatencyにはBestとWorstがあるが、これはLatencyが最も少ない(Best)場合と最も多い(Worst)場合のケースでの集計である。

まずLatencyそのものはBestとWorstでそう大きく違わないが、Bandwidthの方はそれこそ2.5倍(Core i7-6950X)~7.8倍(Ryzen 7 1800X)と大きな開きがある。そしてこの開き、共有キャッシュ構造のCore i7-6950Xだけが2.5倍程度で済み、排他キャッシュ構造のSkylake-SPコアやRyzen 7 1800Xの開きがずっと大きいのは納得できる。

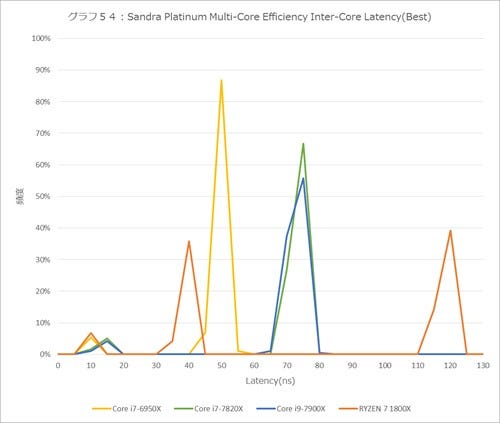

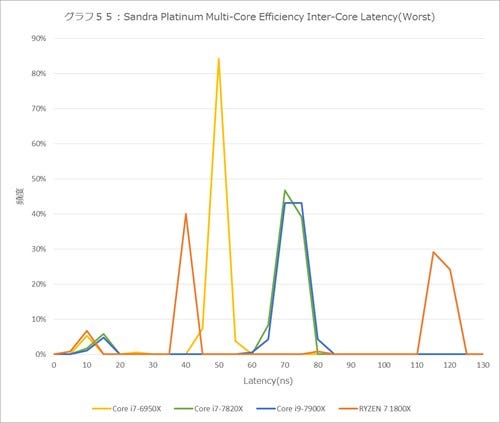

さて、もう少し細かく見てみる。仮想コアで言えば、Core i7-7820XとRyzen 7 1800Xが16コア、Core i7-6950XとCore i9-7900Xは20コアである。16コアの場合、コア間の1:1接続は全部で120pair、20コアの場合は190pairある計算になる。この120pairなり190pair同士での通信のLatencyを個別に調べて、それを5ns刻みの分布図の形にしたのがグラフ54と55である。

例えばグラフ54は、Core i7-6950Xでは5ns~10ns以内のLatencyにおけるpairが5%ほど(実際には10pair)、45~50nsのLatencyのPairが87%(165pair)、40~45nsのPairが7%(13Pair)、50~55nsのPairが1%(2Pair)あるということを示している。

このうち5~10nsのPairというのは、同じコアを共有する2つのThread間のPairのことになる。これはL1~L2レベルで通信できるから最速である。それ以外のケースでは、Core i7-6950Xの場合、Ring Busを経由してコア間通信になるが、この際のLatencyはおおむね40~45nsに収まるということだ。意外にもRing Busに入る段階でLatencyは一意なようで、隣り合うコアだろうが、Ringの両端だろうが、Latencyは5nsの枠内に収まっている。

と言うグラフの読み方を説明したところで、ではSkylake-SPコアは? というと、おおむね70~75nsの範囲に収まっている。ただよく見ると、まず同一コア内にある論理2コア同士のPairのLatencyもちょっと大きく、Inter-Core間のPairは65~70nsと70~75nsの両方に分布している。

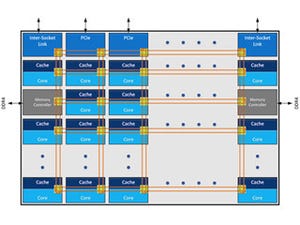

Skylake-SPでは、アーキテクチャが変更になり、従来のRing BusからMesh構造になった、という話はすでに「レポートがある通り」(http://news.mynavi.jp/news/2017/06/16/089/)だが、そのMeshの代償がこの大きめのLatencyである。また同一コア内のPairのLatencyが大きいのは、特にL2でL3との排他制御のチェックのために余分にLatencyが掛かっているのではないかという気がする。

ついでにRyzen 7 1800についても。グラフ53では平均80ns前後のLatencyとあるが、実際には40ns台と120ns台の2つの山があって、その平均が80nsということだ。これについての説明は簡単だ。

Zenアーキテクチャでは、4つのCPUコア+L3で1つのCPU Complex(CCX)を構成している。Ryzen 7では、このCCX2つをInfinityFabricで接続する形態である。そのため、同一CCX内のPairは40ns台で接続できるが、InfinityFabric経由で異なるCCX間のPairを構成すると、Latencyが120ns台になるということだ。全く余談だが、Ryzen ThreadRipperのテストを早くやってみたい。同じくInfinity Fabricで異なるダイ間を接続した場合のLatencyを見てみたいからだ。

話を元に戻す。グラフ54はBest Caseだが、ではWorst Caseでは? ということでグラフ55を見ると、大きくは傾向が変わらない。ただ、Skylake-SPの2製品はバラつきが大きくなっているなど、若干の違いはあるが、むしろBestとWorstの差はBandwidthに出る。

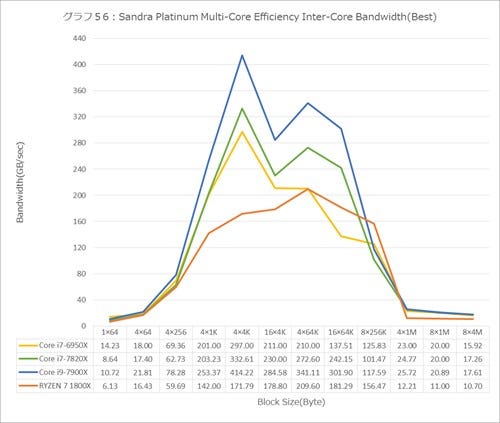

そこででグラフ56がBest caseのBandwidthである。サイズが小さいと当然オーバーヘッドが大きいので効率が悪いが、16KB位のサイズになるとCore i系3製品は性能が良く、Core i9-7900Xでは400GB/sec超えとなる。面白いのはSkylake-SP系はこの後256KBあたりで2つ目のピークを迎えることだ。これはSkylake-SPでL2のサイズを1MBに増やしたことが効果的に効いているものと思われる。

Worst Case(グラフ57)ではどうか? というと、帯域の絶対値が下がるのはともかく、特にSkylake-SP系(+Ryzen 7 1800X)の性能低下が著しい。これはRing BusをやめたためというよりはL3を排他にした影響の方が大きいと思う。そんなわけでアプリケーションの書き方がちょっと変わってくるのは事実ではないかと思う。

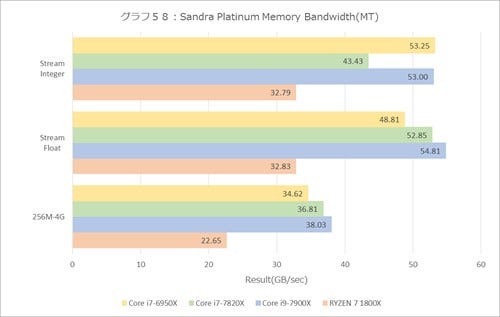

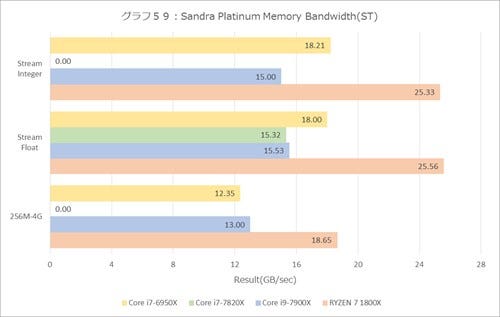

ここからはメモリ周りである。まずはMulti ThreadでStream、およびグラフ60/グラフ61の256MB~4GBの平均値をまとめたのがグラフ58である。ここで見る限り、Core-Xの3製品の帯域は圧倒的である。これはメモリチャネルがRyzen 7 1800Xの倍あるから当然の結果だ。

Single Threadでは? というのがグラフ59である。グラフ36のRMMT Readの結果がここでも再現した。Single ThreadだとRyzen 7 180)Xが最速で、次がCore i7-6850Xであり、Skylake-SP系2製品のコアは全然大したことがない数字になっている。原因についての分析は後でやるとして、RMMTのスコアがここでも再現したことの意味は大きい。

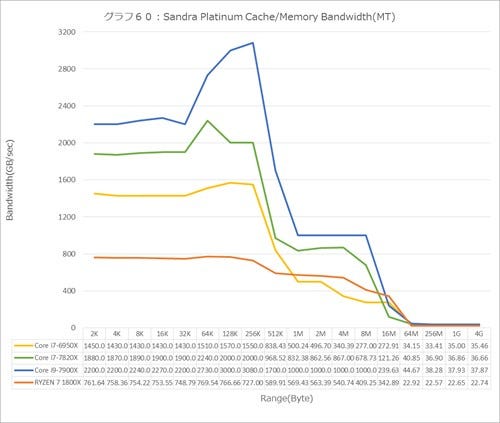

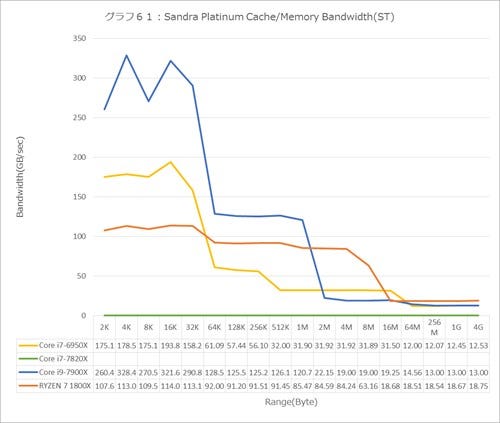

キャッシュを含めた帯域についてまとめたのがグラフ60とグラフ61である。まずMulti Thread(グラフ60)では圧倒的にCore i9-7900Xが高く、次いでCore i7-7820Xと続く、実に分かりやすい構図である。

Single Thread(グラフ61)では、相変わらずCore i7-7820Xのデータが取れていないのだが、ちょっと面白いことに気づく。Core i7-6950Xを基準に考えた場合、Core i9-7900XのL1の帯域は、動作周波数の差を加味しても明らかに大きい。

L2の帯域もCore i7-6950Xの2倍ほどあり、しかもL2の容量が1MBになった関係で、その高い帯域が持続する。問題はL3で、2MB以降を見ると19GB/sec程度だ。同じL3排他構成のRyzen 7 1800Xが4MBまで84GB/sec、8MBでも63GB/secを維持できているのに対して、異様に低い。単にL3排他の影響なのか、それともコア間をMesh接続にしたせいなのかはここでは判断できないが、これはちょっと異様な動きだ。

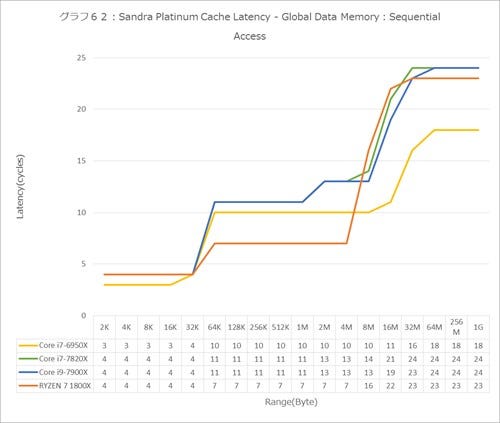

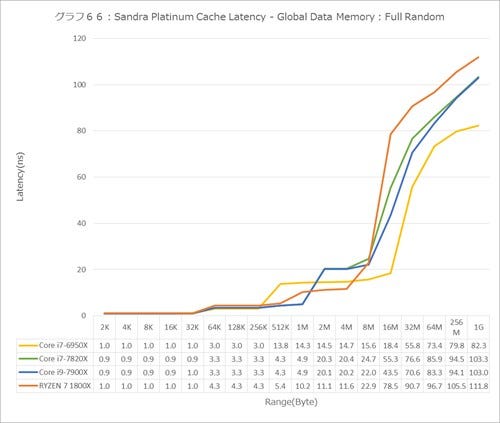

Bandwidthについては以上にして、ここからはLatencyを見てみたい。こちらはMulti Thread/Single Threadの区別がない(というか、Multi Threadでテストを行い、全体の平均値を取る形で実施されているので区別の意味がない)。グラフ62~66がGlobal Data Memoryに対するAccess Latencyである。

Sequential Access(グラフ62)だが、ここは完全Pipeline化されており、うまくPrefetchも動いているようで、1GB RangeでもLatencyは多くない。Skylake-SPの場合、L1は4cycle、L2が11cycle、L3が13cycleということで、すごく多いかと思えば意外と低めに抑えてきた印象ではある。Ring BusのCore i7-6950Xに比べるとややLatencyが多めになっているのはしかたがない。

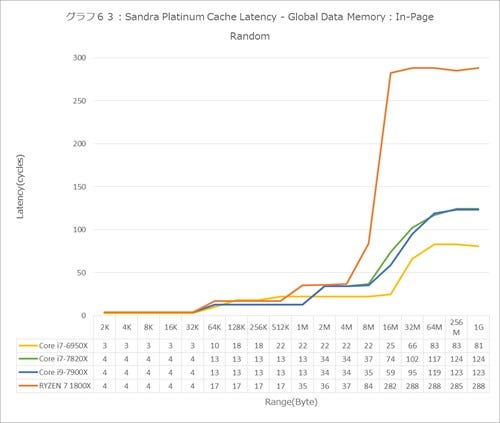

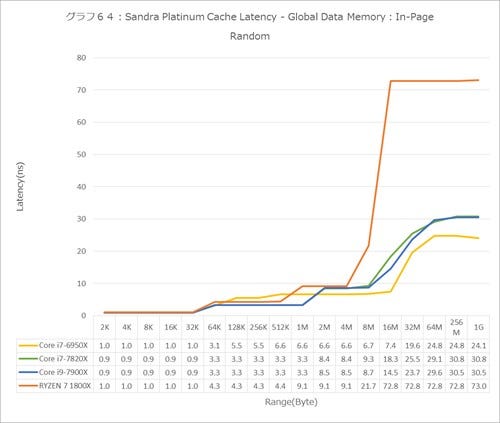

In-Page Random Accessについてまとめたのがグラフ63で、L1が4cycle、L2が13cycle、L2が34cycle、さらにCore i7-6950XよりもLatencyが増えている。L3から先はメモリアクセスになるので、ここは動作周波数の違うコア同士でcycle数を比較しても仕方ない。

そこで実際のLatencyを時間(ns)で示したのがグラフ64である。Core i7-6950Xが24ns程度でアクセスできているのに、Skylake-SPコア2製品はどちらも30ns程度までLatencyが増えており、やはり全体的に見て「Core i7-6950Xよりメモリアクセスが遅い」傾向にある。

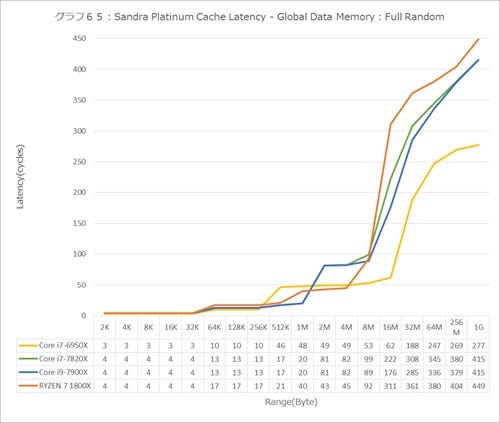

これがもっと極端なのがFull Random(グラフ65~66)である。L3アクセスまではIn-Page Randomと大差ない(グラフ65)が、16MBから先のlatencyを見ると、例えば1GB Rangeでは20nsほども差が出ている。

ちなみにこの結果と、グラフ58の結果は必ずしも矛盾しない。Latencyはリクエストを出してから実際のデータが出てくるまでの時間だし、Bandwidthは一度データが出始めてからの帯域である。

例えば複数のメモリアクセス要求を上手く整理して、なるべく連続してメモリアクセス出来るようにすると、整理に時間はかかる(=Latencyが増える)が、一度アクセスを開始してからは効率よくデータがアクセスできる(=Bandwidthが上がる)。

もしメモリコントローラが、大規模データを上手く扱うように工夫されていると、Latencyが増えてもトータルでは性能が上がる訳で、まさしくSkylake-SPのメモリコントローラはそういう方向で設計されているのではないかと思う。

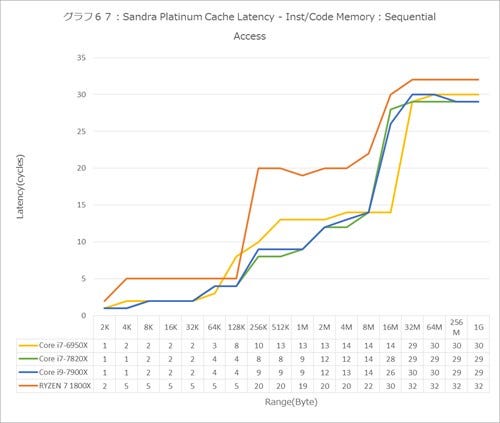

Latencyでもう1つ、Instruction/Code Memoryの結果をグラフ67~72に示す。こちらはロードするのがPrefetch/Fetchユニットで、命令で明示的にアクセスができないという点がGlobal Dataとは異なるところだ。

そしてMicroOps Cacheの存在も無視できない。そのMicroOps Cacheなのだが、Sequencial Access(グラフ67)を見ると、Core i7-6950Xは4K以降が2cycleなのに対し、Skylake-SPは4KBまで1cycleとなっており、Skylake-SPはMicroOps Cacheの容量を増やした可能性がある。

グラフには入れていないが、例えばCore i9-7900Xの場合、測定結果は

| 2KB Range | 1cycle/0.2ns |

| 4KB Range | 1cycle/0.2ns |

| 8KB Range | 2cycle/0.4ns |

| 16KB Range | 2cycle/0.5ns |

| 32KB Range | 2cycle/0.9ns |

| 64KB Range | 4cycle/0.9ns |

となっている。もし8KB Rangeが2cycle/0.5nsになっていれば、単純にMicroOps Cacheの容量が倍と判断できるのだが、これを見ると倍よりももうちょっと多く、その影響もあって8KB Rangeが0.4nsという微妙な数字になっているように考えられるからだ。これが事実なら、最適化へのインパクトはかなりあるはずだ。この辺りの考察は後でまとめて行いたいと思う。

話を戻すと、Skylake-SP系はL1が2cycle、L2が4cycle~9cycle、L3が13~14cycle程度で、Memoryは30cycle前後である。Global Dataに対するアクセスよりもずっとLatencyが少ないのは上手くPrefetchが動作しているためと思われるのだが、謎なのはL2である。Skylake-SP世代ではL2が1MBに増量されたから、64KB~1MBは一定のLatencyでも良いはずなのに、256KBから増える。この原因として考えられるものは

- Prefetcherが旧来のものをそのまま使っていて、1MB L2の対応がうまくいっていない。

- L2のLatencyは実は9cycleだが、先頭32KBに関してはPrefetchが良い仕事をしているので4cycleでアクセスできる

が考えられる。どちらか? と言われたら筆者は後者の案を取りたい。Global Dataの場合、L2のLatencyは13cycleになっており、Instructionでもここから大幅に高速化できるわけではないからだ。その意味では良く頑張ったというべきだと思う。

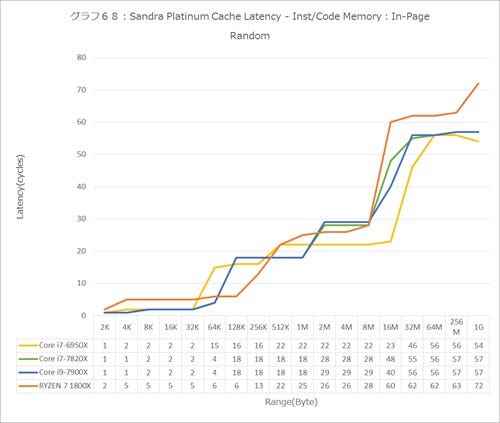

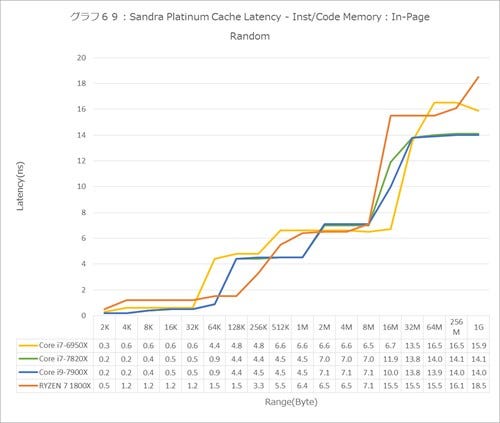

In-Page Random(グラフ68とグラフ69)も傾向は同じである。グラフ68を見ると、64KBは4cycleでアクセスできているのに128KBだと18cycleまで増えているのは、Prefetchでは対応しきれないというあたりであろう。

またグラフ69を見ると、例えば1GB RangeのLatencyはCore i7-6950Xが16cycle前後なのに対し、Skylake-SPの2製品は14cycleに留めており、これもなかなか優秀な結果だと思われる。

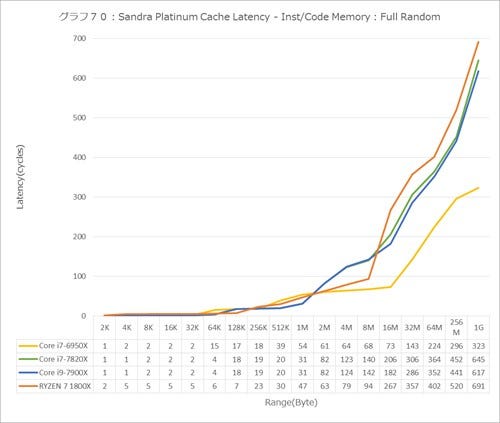

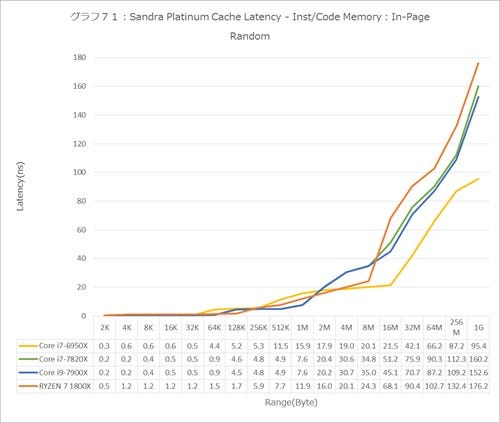

最後がFull Random(グラフ70とグラフ71)。さすがにこのあたりになると、L3のLatencyも大幅に増えており、メモリアクセスもかなり遅い。特にメモリアクセスについて、グラフ71で見るとCore i7-6950Xの倍近いLatencyになっている。要するにメモリコントローラが、ある程度規則的なアクセスパターンを前提に最適化されているということだろう。

もっともGlobal Dataはともかく、Instruction/CodeでRandom Accessというのは普通考えにくい(ない訳ではないが、頻度は低い)ので、これはこれで問題ない気もするが。

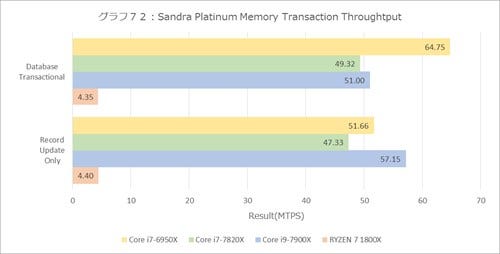

主だったテストはこれで終わりだが、最後におまけを2つほど。まずはMemory Transacition Throughput(グラフ72)である。

Ryzen 7 1800XはIntel TSXに含まれるHLE命令をサポートしていないからソフトウェアロックということで遅いのは仕様通り。問題はCore i7-6950X vs Skylake-SPコアで、Database TranscationだとCore i7-6950Xが最高速というのは、多分メモリアクセスの方法を従来とは少し変えないといけないことを示唆している様に思われる。

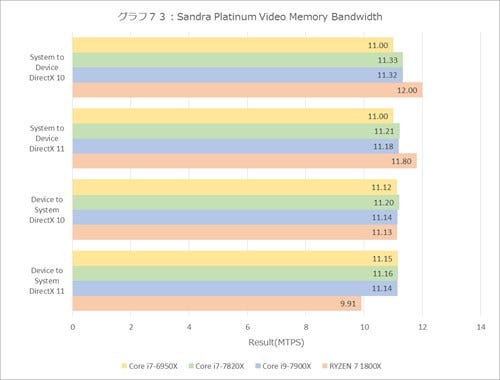

最後がVideo Memory Bandwidthで、これは要するにPCI Express経由の性能である。結果はグラフ73の通りで割と安定した結果になっていることが判った。