米Intelは6月15日(現地時間)、2017年中ごろの投入を予定するデータセンター向けプロセッサ「Xeon Processor Scalable Family」で、CPUコア間やキャッシュメモリのインターコネクトにメッシュアーキテクチャを採用すると発表した。

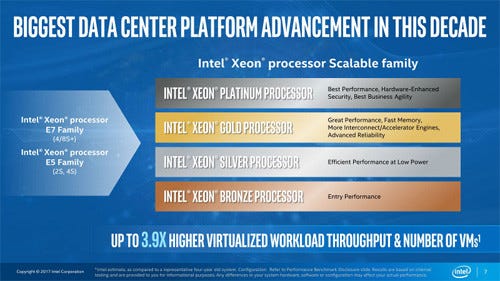

「Xeon Processor Scalable Family」は、2017年5月に公開した新CPUファミリー。従来はソケット数に応じて、Xeon E7/E5/E3とカテゴリーを分けていたところ、パフォーマンスや搭載する機能によって、Xeon Platinum/Gold/Silver/Bronzeとランクを改めるという。

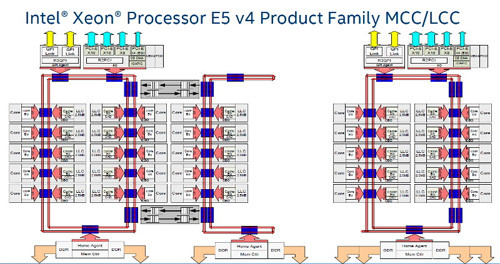

Xeonを初め、Intel製CPUの多くでは、CPUコアやメモリコントローラなどの接続に環状の「リングバス」を採用している。例えば"Boradwell-EX/EP"ことXeon E7/E5 v4ファミリーでは、コア数が10を超えると、リングバスは2つとなり、その間をバッファースイッチで接続する構成をとっていた。この場合、CPUコアが増えるごとにコア同士やI/Oユニットとの距離が生じてしまい、レイテンシが増えてしまっていた。

|

Boradwell-EP(24コア)の構造。単純に隣のコアにアクセスする場合はいいが、リング間をまたいだデータ転送を行おうとすると、かなりのホップ数になる。その分、データ転送にかかるレイテンシや、電力消費は大きくなる |

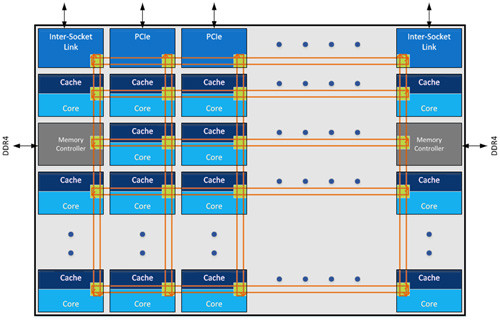

一方、「Xeon Processor Scalable Family」では、新たに2次元のメッシュアーキテクチャを採用。CPUコアやキャッシュ、メモリコントローラ、PCIeを網目のようなタイル状に配置する。CPUコア間やメモリコントローラ、PCIeの間のデータ転送を短い経路で行うことが可能で、バンド幅の増加やレイテンシの低減、電力消費の削減が実現できるという。コアの増加に伴う、電力消費やレイテンシの増大も抑えることが可能だ。

|

Xeon Processor Scalable Familyで採用するメッシュアーキテクチャ。CPUコアやキャッシュ、メモリコントローラ、I/Oユニットをタイル状に配置してその間を接続する。実はメッシュアーキテクチャ自体は第2世代Xeon Phi(Knights Landing)で導入されている |

特にLLC(Last Level Cache)へのアクセスには効果的で、片方のリングにあるCPUコアからもう片方のリングにあるLLCへアクセスする場合、距離があるため、大きな遅延が発生するが、メッシュの場合はこの経路を短縮できる。

気になるのは、コンシューマ向けCPUへの影響だ。従来、Core i7 Extreme Editionのようなデスクトップ向けのハイエンドモデルは、Xeon向けのダイを流用する形で提供してしてきた。IntelがCOMPUTEX TAIPEI 2017で発表した「Intel Core i9」シリーズでも同様にメッシュアーキテクチャを採用するのか。公開されたダイマップでは、これまでとは異なる実装のようにも見えるが、詳細を待ちたいところだ。