I-TLB(グラフ49~72)

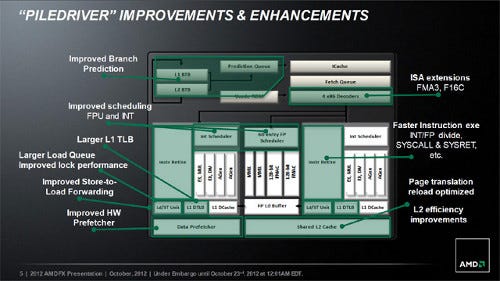

Trinityでの結果はこちら。実はこのTLB周りが良く判らない、というのはTrinityの記事でも触れた通り。Vishera発表字のスライド(Photo01)は、以前のTrinityの際のスライドとほぼ同じであるが、スライド写真を見ると判るとおり、I-TLBのブロックがそもそも描かれていない(笑)。なので、D-TLBはともかくI-TLBがどうなっているのか良く判らないというのが正直なところ。Trinityの際の結果としては、「大きくは変わらないが多少改善を施しているっぽい」という形でまとめさせていただいた。

|

Photo01: Trinity記事との違いは"Larger Load Queue:Improved lock performance"が追加されていること。単にTrinityの時のスライドでは入れ忘れたのか、それともTrinity向けとは若干インプリメントが異なっているのか、までは不明。 |

そもそものFX-8150というかZambeziのI-TLBの構造は、以前こちらで説明した通り、L1 I-TLBが72 EntryのFully Assosiative、L2 I-TLBは512 Entryの4-way Set Assosiative構成である。

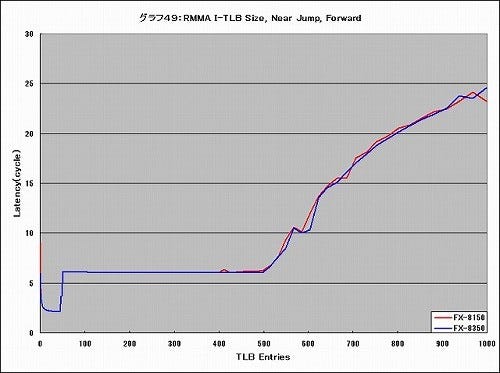

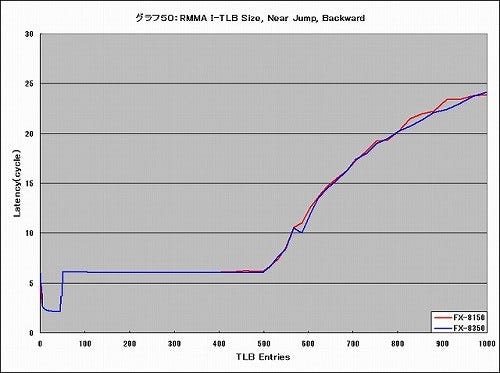

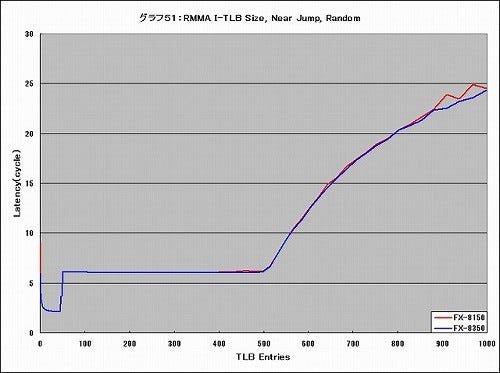

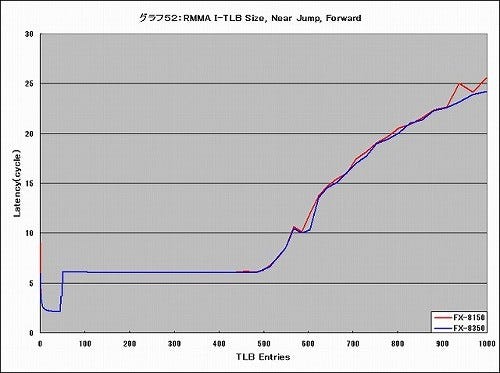

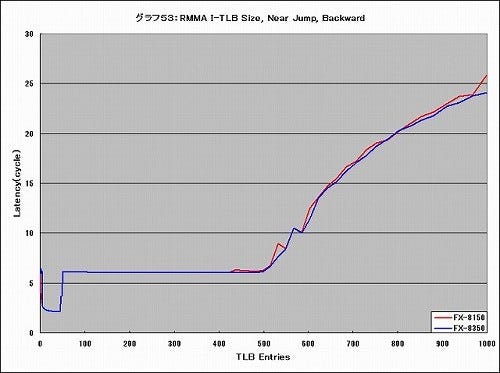

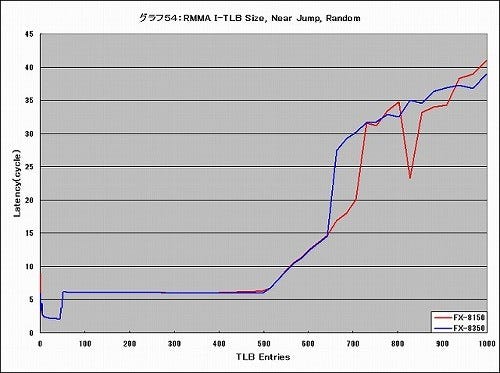

では実際はどうか? ということでまずはTLB Sizeの比較である。グラフ49~51がNear Jump、グラフ52~54がFar Jumpの結果である。まずどのグラフでも、L1 TLBは48前後で溢れ、それをMissするとL2 TLBが512 Entriesまで提供するが、その後は緩やかにLatencyが増えてゆくという構図には変わりがない。なので、絶対的なサイズそのものはFX-8150とFX-8350で同じである、と結論付けて良いと思う。

次ページ:RMMA - I-TLB(その2)