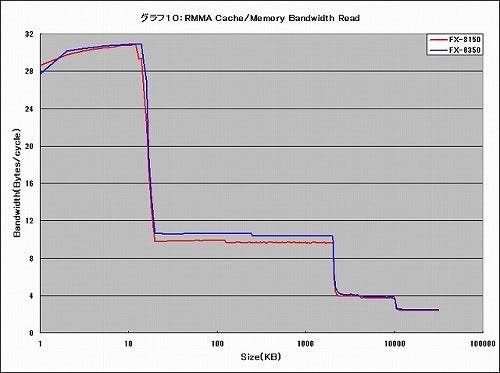

Cache/Memory Bandwidth(グラフ10~12)

次はCache/Memory Bandwidth。Trinityでの結果はこちらである。

まずRead(グラフ10)であるが、こちらはData AccessということでL1はD-Cache側(16KB/Core)のアクセスとなる。理論上は32Bytes/cycleまで伸びるのかもしれないが、結果ではそこまでは行かずに31Bytes/cycle弱程度がピークで、ここはFX-8150もFX-8350も変わらない。続くL2 Cacheであるが、ここはFX-8350が10.6Bytes/cycle程度、FX-8150は9.7Bytes/cycle程度となっており、Data L1-L2間のThroughputもさらに高速化された形だが、これはData L1-L2間を高速化したのか、それともL2そのものを高速化したのか、まではこの結果から読み取れない。ただInst L1-L2間は3.7Bytes/cycle→5Bytes/cycleで35%ほど高速化したのに、Data L1-L2間は9.7Bytes/cycle→10.6Bytes/cycleで10%弱の高速化でしかないあたり、PiledriverではData ThroughputよりもIPCの向上を目指したとは言えるだろう。

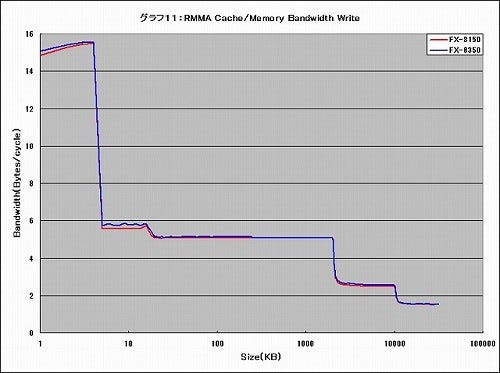

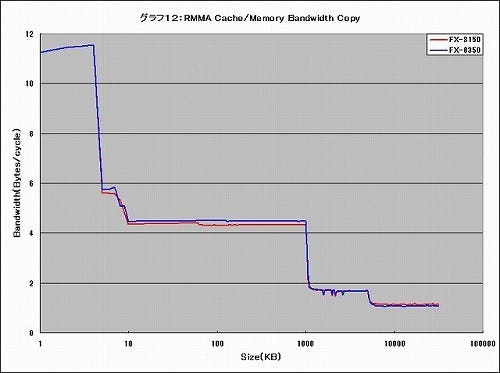

Write(グラフ11)・Copy(グラフ12)も若干の改善は見られるが、これは大きな性能差とは言いにくい。専らReadの高速化により、Copyでも若干の性能改善が実現できたという程度であろう。