デバイスの磁気耐性 - 外部磁場の向きの役割

MRAMデバイスの動作は完全に電気的に制御されているが、外部の磁場によってデバイスのパフォーマンスが簡単に損なわれる可能性がある。

この信頼性の問題により、磁気耐性に関するより広範な世界規模の調査が始まった。この研究の目的は、作用するメカニズムをより深く理解し、保護を向上させるためのMRAM設計を導くことである。さらに磁場に対するMRAMの堅牢性を認定するためのアプリケーション依存の標準が開発され、保存されたデータが保護される磁場の強度が指定されている。

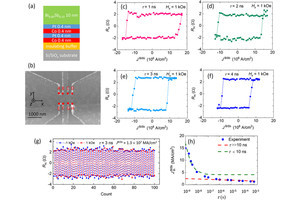

imecは、IEDM 2024で、外部磁場の強度だけでなく方向もMRAMデバイスのアクティブ書き込み磁気耐性に悪影響を与え、WERの劣化として観察される可能性があるという最初の実験的証拠を提供した[8]。

この研究はSTT-MRAMデバイスで実施されたが、主な結論はSOT-MRAMデバイスにも有効であると期待されている。実験では、垂直MTJスタックにさまざまな角度で外部磁場(4~40mT)を印加し、WERへの影響を測定した。特定の外部磁場角度では、10mTという低い磁場でも書き込み信頼性の大幅な低下が観察された。

この実験は、以前の理論的発見とうまく結び付けられた。この知見は、実際のアプリケーションで角度依存のWER劣化の影響を受けにくいMTJスタックを開発する設計者に役立つことが期待される。

アレイレベル - 微細化されたSOT-MRAMデバイスの統合に成功

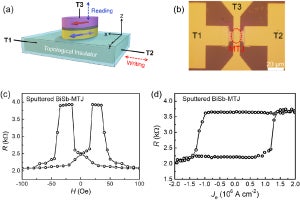

残されたステップは、最適化されたSOT-MRAMデバイスをロジック回路とともに大規模なアレイに統合する可能性を実証することである。VLSI Symposium 2024で、imecはデバイスレベルでうまく機能することが証明されているさまざまなSOT-MRAM構成の特性評価プラットフォームとして機能する機能アレイを発表した。このアレイはさらに汎用性が高く、STT-MRAMの特性評価にも使用できる[9]。

例えば、imecはアレイを使用して、SOTトラックの寸法を縮小することで極限までスケールアップされたSOT-MRAMデバイスの特性を評価した。

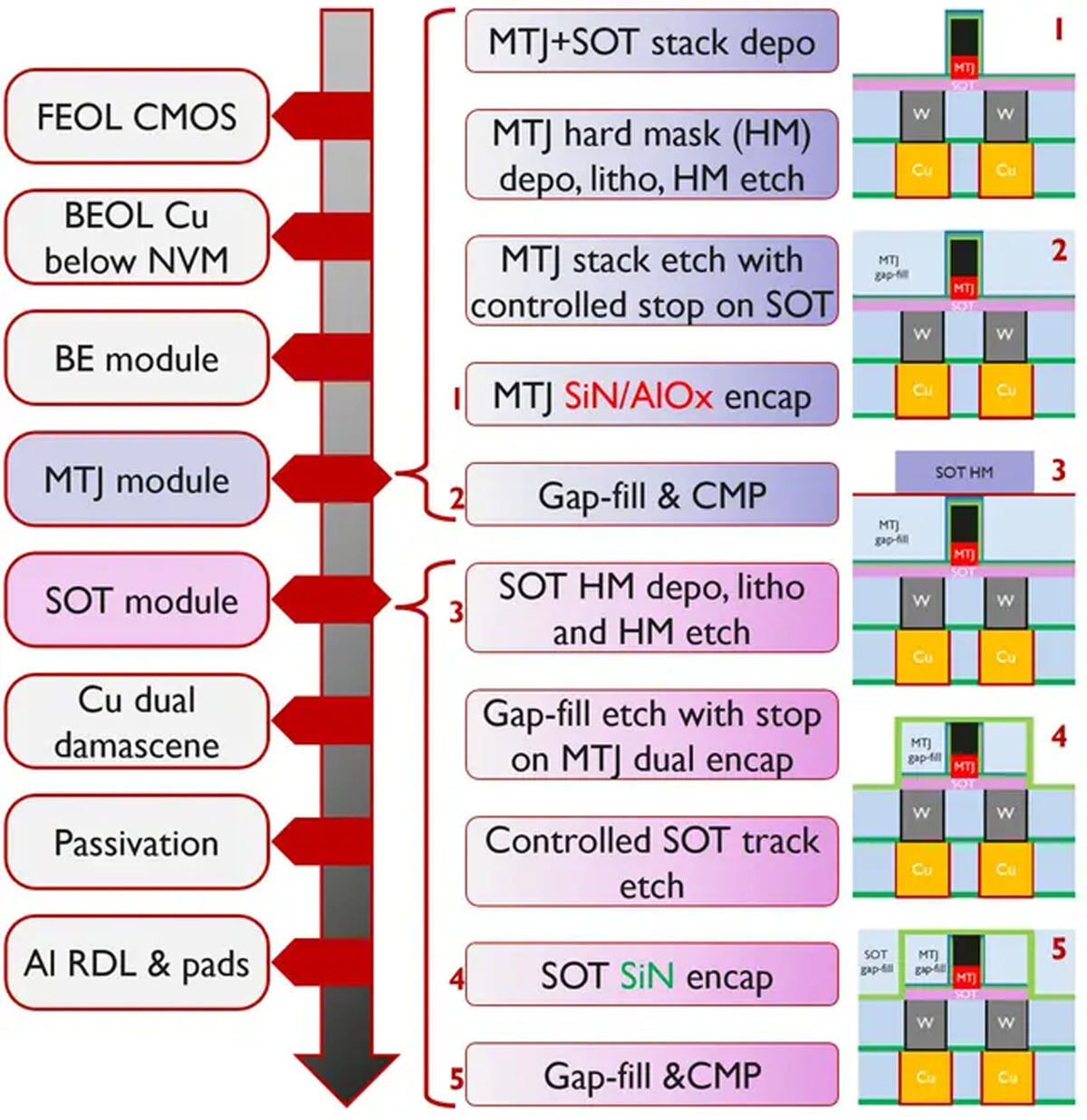

すでに説明したように、これらのデバイスはデバイス レベルでは良好に動作し、スイッチング エネルギーと耐久性が向上している[5,6]。デバイス統合プロセスフローでは、MTJピラーの形成後にSOTトラックをパターン化する必要がある。SOTトラック幅がピラーの直径まで縮小される極端にスケールアップされたデバイスでは、連続するSOTパターン化ステップによってピラーの側壁が簡単に露出して損傷する可能性がある。imecの研究者は、この問題を解決するための新しい統合ソリューションを提案した。彼らは、SiNとAlOxの両方を使用してMTJピラーを二重にカプセル化することで、アレイレベルでの読み取りウィンドウなどの重要なパフォーマンスパラメータに影響を与えることなく、SOTモジュールプロセスステップ中に構造を保護できることを示した[9]。

MRAMデバイスを大規模なアレイに統合すると、複雑さが増してしまう。つまり、数千、あるいは数百万のビットセルすべてが、周辺回路内で均一に動作するトランジスタにまったく同じように応答する必要がある。imecでは現在、これらのデバイスの変動を少なくする仕組みを研究している。

結論

SOT-MRAMデバイスは、最終レベルキャッシュアプリケーションでSRAMを置き換える可能性のある候補として認識されている。

imecでは、その実現に向けて残された課題のいくつかに対処し実用的な仕様に近づけた。MTJ材料スタックの再設計により、デバイスレベルでのスイッチングの信頼性が向上し、外部の磁気の影響に対する堅牢性が向上したほか、磁気耐性の補足的な研究により、外部の磁場からデバイスを保護する方法に関する有用な洞察が得られた。さらに機能アレイの実証は、実際に商用利用に向けたマイルストーンとなったといえる。

本記事はimecのResearch update「Bringing SOT-MRAM technology closer to last-level cache memory specifications」をimecの許可のもと、翻訳・改編したものとなります

参考文献

[5] ‘Advancement in perpendicular SOT-MRAM technology for low power and high density embedded applications', S. Van Beek et al., IEDM 2023

[6] ‘Imec's extremely scaled SOT-MRAM devices show record low switching energy and virtually unlimited endurance', imec press release 2023

[8] ‘Magnetic immunity of STT-MRAM: external magnetic field orientation impact on writing reliability’, N. Vander Meeren et al., IEDM 2024

[9] ‘Extremely scaled perpendicular SOT-MRAM array integration on 300mm wafer’, F. Yasin et al., VLSI 2024

Farrukh Yasin(ファルーク・ヤシン)

Van Dai Nguyen(ヴァン・ダイ・グエン)

Simdharth Rao(シッダールト・ラオ)

Gouri Sankar Kar(ゴーリ・サンカル・カル)