メモリコミュニティは近年、SOT-MRAM技術の開発で大きな進歩を遂げてきた。

imecも画期的な改良でこの進歩に貢献してきた。VLSI Symposium 2018での最初の発表に続いて、キャッシュアプリケーションへの道のりにおける主要な課題に対処するための進歩的なイノベーションを報告している[1,2]。

これまでに、300psまでのスイッチング速度を備えた最先端のSOT-MRAM単一デバイスが300mmウェハ上で実証されている[3,4]。垂直MTJ磁化の採用は、スケーリングの可能性を向上させるための重要なステップであると考えられている。

また、書き込み操作中に外部磁場を必要としないことで、SOT-MRAMの技術準備レベルの向上にも進展があった。このような磁場は、確定的な磁化スイッチングを保証するために必要である。外部磁場がないと、書き込み操作の信頼性が低下し、書き込み成功率は50%になってしまう。製造の観点から、外部磁場を使用してメモリデバイスを操作することは、製品レベルでは実現可能ではない。したがって、磁場フリーのSOT-MRAMデバイス技術の開発が不可欠となる。imecの研究者たちは、SOTトラックの一部として面内磁性層を組み込むことで、磁場フリーのスイッチングアプローチを実証した。この磁性層によって誘導される面内磁場が外部磁場の役割を引き継ぎ、技術の実用性を高めている[3,4]。

フリー層の磁化を切り替えるために必要な高い注入電流に関連する動的消費電力を下げるためのソリューションも提案されている。IEDM 2022では、書き込み操作中に電圧ゲート支援アプローチを実証し、切り替えのエネルギー障壁を下げたことを報告した[3,4]。電圧ゲート支援アプローチはビットセル面積の削減も可能にし、高密度SRAMアプリケーションにとって魅力的である。

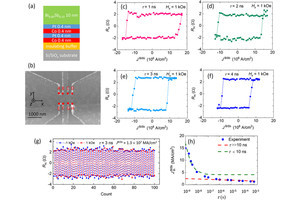

スイッチングエネルギーは、SOTトラックの寸法をスケーリングすることでさらに改善できる可能性がある。従来のSOT-MRAM設計では、オーバーレイプロセス制御に十分なマージンを確保するために、基礎となるSOTトラックが占める領域は実際のMTJピラーのフットプリントよりも大きくなっている。しかし、注入電流の一部がMTJ領域の外側に流れるため、エネルギーが無駄になってしまう。IEDM 2023で、imecの研究者たちはSOTトラックとMTJピラーのフットプリントが同等になるようにSOT-MRAMデバイスを極限までスケーリングできることを示した。これは、大きなビットセル密度に向けたマイルストーンである[5,6]。これらの単一デバイスでは、ビットあたり100fJ未満のスイッチングエネルギーと、1015回を超えるプログラム/消去サイクルの耐久性が実証された。

今後はMRAMのパフォーマンスと信頼性の向上、アレイの集積が進む

SOT-MRAMのスイッチング速度や耐久性などの主要な仕様は達成されているが、材料スタックを再設計することで、保持、BEOL互換性、外部磁気の影響に対する堅牢性、書き込みエラー率(WER)などのパフォーマンスと信頼性のパラメータをさらに最適化する機会が生まれた。WER は信頼性に関する重要な懸念事項であり、書き込み電流が印加されたときに強磁性フリー層が切り替わらない確率を指している。

さらに、研究の取り組みは主にデバイスの改善に焦点を当てているが、産業への導入に向けた重要なステップは、スケーリングされたSOT-MRAMデバイスの大規模アレイ集積である。これらのアレイデモンストレーターでは、多くのメモリビットセルが、読み取りおよび書き込みアクセスを提供し、ビットセルに電流と電圧を出し入れするトランジスタを含む基礎回路に接続されている。

デバイスの改善とアレイの統合により、テクノロジーは現実世界の仕様に近づいた。これらすべての問題に対処するには、通常、さまざまなパラメータ間のトレードオフが必要になる。VLSI Symposium 2024およびIEDM 2024でimecが報告した最新の研究では、シミュレーションによる統合の最適化と材料およびデバイスの再設計を通じて、可能な限りの改善に重点が置かれた。

デバイスレベル - 新しいフリー層スタックでSOT-MRAMデバイスのスイッチングの信頼性が向上

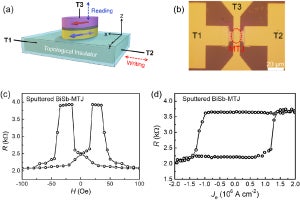

IEDM 2024で、imecはMTJ用の革新的な複合フリー層を提案し、SOT-MRAMデバイスのより信頼性の高いスイッチングを実現した[7]。この新しいフリー層スタックは、合成反強磁性(SAF)構造、つまりRu層を介して反強磁性結合された2つの強磁性層で構成されている。

このシステムは、TMR読み出し用の従来のCoFeB層に集積されている。この新しいスタックにより、TMR(読み出し操作に重要)とSOTスイッチング操作(書き込み操作の効率をさらに向上させるパスを提供)を個別に最適化できるようになった。

-

従来のMTJスタック(左)とSAFベースのフリー層(FM1/Ru/FM2)を備えたMTJスタック(右)の概略図。SAF構造の上部のフリー磁性層FM2は、TMRを使用したSAFの電気的読み出しのためにCoFeB/MgOと強磁性結合している (IEDM 2024で発表)

この工夫により、初めて10-6という目標仕様を満たすことができた。従来のフリー層を備えたデバイスと比較して、データ保持はΔ~50から90に改善された。読み出し側では、SOTスイッチング動作に影響を与えることなくTMRをさらに拡大することができた。さらに、複合フリー層は磁気特性を維持しながら400℃までの温度に耐えるため、BEOL処理と互換性がある。SAFフリー層により、SOT-MRAMデバイスは外部磁気摂動の影響を受けにくくなった。

この研究では、imecの研究者たちがマイクロマグネティックシミュレーションを使用して材料スタックの設計を導き、最適な結果を導きだした。シミュレーションと実験の組み合わせは、SOT-MRAM技術の進歩に不可欠である。

(次回に続く)

本記事はimecのResearch update「Bringing SOT-MRAM technology closer to last-level cache memory specifications」をimecの許可のもと、翻訳・改編したものとなります

参考文献

[1] ‘SOT-MRAM 300mm integration for low power and ultrafast embedded memories', K. Garello et al., 2018 IEEE Symposium on VLSI Circuits

[2] ‘Recent progress in spin-orbit torque magnetic random-access memory', V. D. Nguyen et al., npj Spintronics 2, 48 (2024)

[3] ‘First demonstration of field-free perpendicular SOT-MRAM for ultrafast and high-density embedded memories', K. Cai et al., IEDM 2022

[4] ‘Novel SOT-MRAM architecture opens doors to high-density last-level cache memory applications', imec Reading Room article 2023

[5] ‘Advancement in perpendicular SOT-MRAM technology for low power and high density embedded applications', S. Van Beek et al., IEDM 2023

[6] ‘Imec's extremely scaled SOT-MRAM devices show record low switching energy and virtually unlimited endurance', imec press release 2023

[7] ‘Achieving 1ppm write-error rate in SOT-MRAM with synthetic antiferromagnetic free layer', V.D. Nguyen et al., IEDM 2024

Farrukh Yasin(ファルーク・ヤシン)

Van Dai Nguyen(ヴァン・ダイ・グエン)

Simdharth Rao(シッダールト・ラオ)

Gouri Sankar Kar(ゴーリ・サンカル・カル)