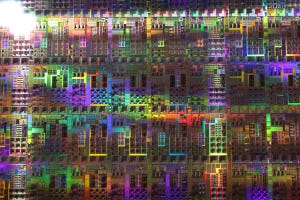

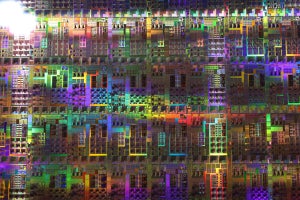

SOT-MRAMメモリデバイスの基本的な構成要素

MRAM(Magnetoresistive Random Access Memory:磁気ランダムアクセスメモリ)は文字通り、磁化の方向によって記憶素子の電気抵抗が変わることを利用した不揮発性メモリである。その中でも次世代MRAMとして期待されているSOT-MRAM(Spin Orbit Torque MRAM:スピン起動トルク磁気RAM)は、最終レベルキャッシュメモリとして使用するための興味深いパフォーマンスと信頼性の特性を備えている。

デバイス設計をさらに最適化することで、書き込み電力消費、デバイス密度、および寿命を向上させることができ、これらの進歩をアレイレベルで実現することで、実際のアプリケーションにさらに近づくことができる。

材料スタックの再設計、極小型のSOT-MRAMデバイスの大規模アレイ統合、磁気耐性の理解を深めることで、imecがこれらの問題にどのように対処したかを、VLSI Symposium 2018からIEDM 2024に至る国際会議での発表を基に、imecより翻訳の許可を得る形で、ベルギーimecでMRAMの研究に従事している担当者らが示した内容を複数回に分ける形で紹介する。

SOT-MRAMが将来のキャッシュメモリでSRAMを置き換えることができる理由

超高速で揮発性のSRAMは、何十年もの間、高性能コンピューティングアーキテクチャの組み込みキャッシュメモリとして使用されてきた。このメモリは、プロセッサのすぐ近くにあり、マルチレベル(L1、L2、L3……)の階層システムである。その役割は、頻繁に使用されるデータと命令を保存して、すばやく取り出すことである。L1は、すべてのキャッシュメモリの中で最も高速である。SRAMのビット密度のスケーリングはしばらく前から鈍化しており、ビットセルはますますスタンバイ電力の問題に悩まされている。

SOT-MRAMメモリソリューションには、スタンバイ時の消費電力が低い、GHzレベルのスイッチングまたは書き込み速度、リークが無視できる、実質的に無制限の耐久性、高い信頼性、スケーラビリティなど、いくつかの利点がある。これらの理由から、業界では、組み込み最終レベルキャッシュメモリアプリケーションにおけるSRAMの有望な代替手段としてSOT-MRAMの評価が高まっている。

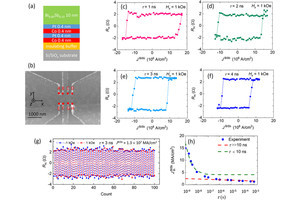

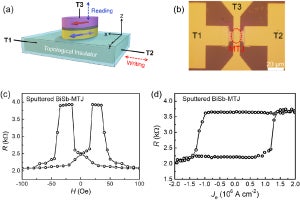

SOT-MRAMメモリデバイスの基本的な構成要素は、磁気トンネル接合(MTJ)である。これは、2つの強磁性層(CoFeBベース)の間に挟まれた薄い誘電体層(MgO)で構成されている。強磁性層の1つは固定(またはピン留め)された磁気を持ち、もう1つの層はZ軸に沿って自由に回転する磁気を持っている。強磁性層の磁化方向は、層の平面に対して垂直または平行のいずれかであり、それぞれ垂直MTJおよび面内MTJと呼ばれる。

SOT-MRAMメモリビットセルは、MTJに電流を流し、接合部のトンネル磁気抵抗(TMR)を測定することで読み出される。TMRは、自由層と固定層の磁化の相対的な向き(つまり、平行=“1”または反平行=“0”)に応じて、高くなったり低くなったりする。

メモリセルへの書き込みは、スピン偏極電流をMTJに注入し、スピン軌道相互作用によって自由層の磁化を切り替えることで行われる。電流注入はMTJの下の横方向に、隣接するSOT層(またはSOTトラック)(通常はタングステンなどの重金属)を介して行われる。そのため、読み取りパスと書き込みパスは分離され、信頼性の高い動作が保証される。この書き込み操作において、SOT-MRAMは、書き込み電流がMTJに垂直に注入される別のMRAMであるSTT-MRAMとは異なる。STT-MRAMの書き込み操作中、大量の電流がMgOバリアを通り抜ける。

(次回に続く)

本記事はimecのResearch update「Bringing SOT-MRAM technology closer to last-level cache memory specifications」をimecの許可のもと、翻訳・改編したものとなります

Farrukh Yasin(ファルーク・ヤシン)

Van Dai Nguyen(ヴァン・ダイ・グエン)

Simdharth Rao(シッダールト・ラオ)

Gouri Sankar Kar(ゴーリ・サンカル・カル)