前回は、半導体製造の8工程のうち2つ目にあたる酸化工程を取り上げ、ウェハを強力に保護する酸化膜がどのように作られるかについて紹介しました。

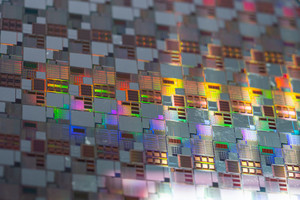

さて、ウェハの表面に酸化膜が作られたので、半導体にするためにウェハに回路を描く必要があります。リソ工程は、銀塩カメラの写真撮影と同じように、ウェハに回路を焼き付ける工程です。今回は、3つ目の工程となる「リソ工程」を紹介します。

リソ工程とは?

リソ工程は“フォトリソグラフィ”を略した呼び方です。「フォト」と「リソグラフィ」を組み合わせた名称で、光を使ってウェハに回路を焼き付けます。つまり、半導体を製造するためにウェハに平面図を描く工程と考えてください。精度が高く微細な回路パターンを描くには、集積度が高いほど高水準のフォト工程技術が必要になります。

リソ工程は、フォトレジストの塗布、露光、現像で構成されます。それでは各ステップを見てみましょう。

1:フォトレジストの塗布

ウェハに回路を描くための第1ステップは、酸化膜にフォトレジストを塗布することです。フォトレジストは、化学変化してウェハが印画紙の役割を果たすようにする物質です。ウェハの表面に塗布するフォトレジストが薄く、均一であるほど、高品質な回路パターンを焼き付けることができます。このステップでは、スピンコーティングと呼ばれる方法を用います。

フォトレジストは、光(UV光)に対する反応に応じて、露光していない領域が残るポジ型フォトレジストと、露光した領域が残るネガ型フォトレジストに分けられます。ポジ型フォトレジストは、光を照射した領域のみが腐食して消えますが、ネガ型フォトレジストは光を照射した領域のみが重合したままの状態になります。

2:露光

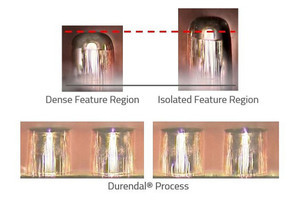

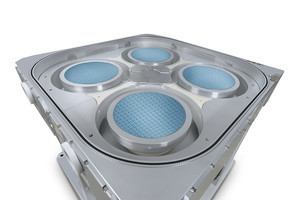

ウェハにフォトレジスト膜が形成されたら、光を当てて回路を焼き付ける露光処理に進みます。この時、露光装置を使って選択的に光を通過させます。回路パターンの付いたマスクを光が通過すると、フォトレジスト膜が形成されたウェハに回路が焼き付けられます。

露光処理で焼き付けられた回路パターンが小さく精密であるほど、多くの素子をチップに構成できるため、生産効率が高まり、素子当たりのコストが低減されます。その結果、EUVリソグラフィ(極端紫外線リソグラフィ:微細化がさらに進み、半導体チップの生産性を向上させる次世代のリソグラフィ技術)という最新技術が注目されています。2020年初めに、ラムリサーチは、ASMLと半導体研究機関であるimecとの戦略的パートナーシップを通じて、EUV露光処理時の歩留まりと生産性を向上させる新しいドライレジスト技術を発表しました。これは、解像度を上げることによって回路の幅を微調整する鍵となる技術です。

3:現像

露光処理が完了したら、半導体回路パターン以外の部分からフォトレジストを選択的に取り除くためウェハに現像液を噴霧して、半導体回路パターンを形成する現像処理を実行します。現像処理の後、さまざまな測定機器や光学顕微鏡で検査して回路パターンが十分に描かれているかどうかを確認し、フォト工程が完了します。

フォト工程に関連した用語を以下で説明します。次回は、半導体回路を焼き付けるフォト工程の後の第4工程であるエッチングについて説明します。

フォト工程関連用語

- 露光:半導体製造工程において選択的に光を照射することです。

- 集積度:チップ当たりの素子数で、ダイオードや抵抗、トランジスタなど、チップ上に構成される論理素子数を表します。

- スピンコーティング:液体を薄く広げるために高速で回転させるコーティング方法です。

- マスク:集積回路または透明な負性素子の構造を持つガラスプレートで、半導体に回路を焼き付けるために使用されます。あるいは、ウェハの特定の領域を保護すると同時に他の領域を処理する物質の層を指すこともあります。

- 解像度:顕微鏡などで、物体の微細像を再現するレンズ能力、または像の微細部分を特定するレンズ能力を指します。

(次回は12月に掲載します)