IntelのSpring Hill

Hot Chips 31においてIntelは、推論処理用の「Spring Hill」を発表した。Spring Hillは既発表であるが、正式な学会での発表ということで、これまでの発表に比べてより詳しい発表が行なわれた。

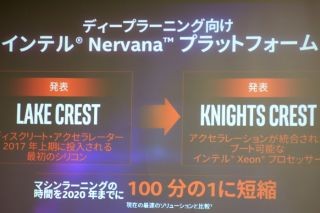

Spring Hillは「NNP I-1000」というのが正式名称で、NNPはNeural Network Processorの略でIはInference(推論)用であることを示している。発表者は、Intelのイスラエルの開発チームのIntel FellowであるOfri Wechesler氏である。学習用のSpring Crestもイスラエルチームの開発であるが、Spring CrestはNervanaのチームが買収されてからも開発を続けたようであるが、Spring Hillの方はx86コアを搭載しているように、Intelのx86系の開発チームが担当したと思われる。

Spring Hillの開発目標は、データセンタの推論処理において最高の性能/電力効率を達成することで、具体的には4.8TOPS/Wという値が掲げられている。そして、用途に応じて、速度優先、低電力優先といった使い方ができるように、消費電力が10W-50Wの範囲で高い効率が出せるというのが2番目の目標である。

3番目の目標は、性能/電力を犠牲にせず、高いプログラム性をもつことである。4番目は、大規模なデータセンタでの使用がターゲットであるので、高度なRAS機能をもつことが要求される。そして、5番目は、すべての主要なディープラーニングのフレームワークをサポートする高機能なソフトウェアスタックを持つことである。

次の図の右上に写っているのがSpring Hillであるが、M.2というフォームファクタとなっている。M.2はSSDのパッケージとしてよく使われており、小型のPCIeボードよりもずっと小さく、物理的には多くのDLエンジンをサーバに載せることができる。

なお、M.2フォームファクタでは50Wの電力は無理で、Intelは色々なフォームファクタのSpring Hillを作る計画である。

-

Spring Hillはデータセンタ向けの推論エンジンで、4.8TOPS/Wという高い性能/電力を開発目標に置いている。そして、データセンタでの大量使用に耐えられるRAS機能を持つことも設計目標である (出典:この連載のSpring Hillの部分の図は、すべてHot Chips 31でのIntelのOfri Wechesler氏の発表スライドのコピーである)

Spring HillはIntelの最新の10nmプロセス(他社の7nmプロセスに近いサイズ)で作られており、内蔵するIAコアは最新のSunny Cove(SNC)コアである。そして、Spring Hillは、1個のIAコアと6個のICEと書かれたInference Compute Engineをまとめたものが1つのグループで、それが2グループあるという構成になっている。IAコアは512bitベクトルを扱うAVX-512命令やディープラーニング用に追加されたVNNI命令をサポートしている。

Spring Hillは、24MBという大容量のLast Level Cacheを持っている。このキャッシュはハードウェアでコヒーレンシが維持されているので、IAコアもICEも同じデータが見えるので使いやすい。

多分、8個のSNCコアを搭載するチップから6コアを12個のICEに置き換えているので、もともと、CPUコアのキャッシュ間のコヒーレンシ機構は入っており、Spring Hillを作るときにもそのまま使っているだけという見方もできる。

メモリインタフェースはLPDDR4を2チャネル持ち、最大4.266GT/sの転送を行えるので、最大68GB/sのバンド幅を持つ。I/OはPCIe Gen3 でx4とx8を持っている。

そして、Spring Hillは、電源のレギュレータを内蔵するFIVR(Fully Integrated Voltage Regulator)を使っている。

FIVRは外付けの電源LSIに比べて電源系統を増やしやすく、きめ細かい電源制御ができる。また、電源の応答が速いので、消費エネルギーの削減効果が大きいと考えられる。また、FIVRの使用で外付けの電源ICが不要となったので、M.2のサイズに収まったともいえる。

右下の表に性能などがまとめられている。演算性能はINT8で最大92TOPSとなっている。M.2フォームファクタの推論アクセラレータで、この数字は驚異的である。Intelの10nmプロセスで4000個のINT8 MAC演算器を詰め込んでいるのが効いている。

TDPは10-50W、TOPS/Wは2.0-4.8となっており、50Wの電力の時は2.0TOPS/Wであるから掛け算では100TOPSとなるが、まあ、誤差の範囲であろう。一方、10Wの時は4.8TOPS/Wで、48TOPSで計算は合っている。

Spring Hillは、24MBのLLCに加えてICE内部にもいくつものメモリをもっており、チップ全体に内蔵するメモリは合計75MBにのぼる。

Intelからの発表は無いが、スライドの右上の写真の中央のパッケージには大小2個のチップが搭載されている。大きいほうはSpring Hill本体であるが、筆者は小さいほうのチップはFIVRチップではないかと思っている。10nmプロセスでFIVRのアナログ動作をするトランジスタを作るのが難しく、別チップとしたのではないかと思われる。

-

Spring HillはIAコアとICEと呼ぶ推論コア6個のグループを2つ持っている。そして、24MBという大きなLLCが付いている。それ以外にも大きなバッファがいくつもあり、全部で75MBのメモリを搭載する。そして、Spring Hillは電源にFIVRを使っており、これも電力低減に効いている

(次回は10月4日に掲載します)