CMOS技術が性能、電力効率、そして価格のバランスを取り続けることを可能にしたのは、プロセスの微細化が継続的に進められてきたことが背景にあるとimecは指摘している。しかし近年、さまざまなアーキテクチャやアプリケーションにおける演算要件が爆発的に増加しており、CMOS技術は前例のないスケーリングとコストの課題に直面するようになってきた。

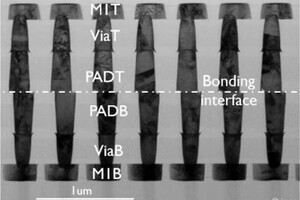

この課題の解決には、既存のパラダイムを再構築する必要があり、imecでは、ヘテロジニアス・パッケージング(異種チップの2/2.5/3次元実装)の代わりにモノリシック・ヘテロジニアス・オンチップ・インテグレーション(半導体チップの上に別の異種チップを載せることを繰り返してあたかも1つのモノリシックチップのような構成にしたチップ多重積層構造)を次世代技術として実現することを目指しており、このヘテロジニアス・インテグレーションの新たなアプローチを「CMOS 2.0」と呼び提案している。

imecでは、半導体産業がモノリシックなSoCの限界に対処するために、CMOSのスケーリングからCMOS 2.0へと進化すべきであると主張しており、それは高度な3D相互接続技術とシステム技術の同時最適化により実現できるとしている。

imecの研究者たちがCMOS 2.0がもたらすパラダイムの再構築についての解説がオンラインジャーナルの「Nature Reviews Electrical Engineering」にて公開された。ここで語られている話は、かなり概念的なものであり、本題に入る前に、CMOS 2.0とは具体的にどんなものであるのか、2024年5月にベルギーで開催された「ITF World 2024」におけるimec CEOのLuc Van den hove氏の基調講演で示された例を紹介しておく。

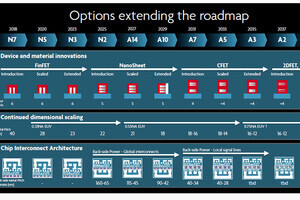

ITF World 2024においてCMOS 2.0というのは、機能や微細化の度合いの異なる複数の異種チップを垂直方向に積層するという概念だと説明されていた。例えば、機能の異なる2種類のメモリチップ、機能とトランジスタ密度・微細化の度合いの異なる2種類のロジックチップ、裏面電源配線網チップ、微細化の度合いが低いI/Oチップがあったとして、それらを垂直方向に積層することで1つのチップを実現する。imecの研究者たちは、裏面電源供給網チップの登場で、CMOS 2.0の実現性が高まっていると説明している。

CMOS 2.0では、垂直方向のみならず、水平方向にも一部の機能を配置することも可能だとしている。例えば、占有面積がチップの一部だけでよいアナログ回路やニューロモフィック・プロセッサを部分的に配置しても良いという。これは脳神経系の可塑性(新たなネットワークを築き生まれ変わる性質)に通じるところがあるとLuc Van den hove氏は強調していた。

物理的限界が見えてきたCMOSプロセスの微細化

CMOS技術は、SoCというパラダイムにより、複雑化するシステムを汎用的なアプローチで駆動させることを可能年、1つのチップに多くのトランジスタを統合することでその性能を向上させてきた。この技術をけん引してきたのは、半導体チップ上に搭載される回路素子(主にトランジスタ)を小型化することで、その搭載数を増加させ、素子当たりのコスト低減を図る、いわゆる微細化であり、過去数十年にわたってCMOSが活用されてきたのは、この継続的な回路素子の小型化と汎用設計が可能であったためだと言える。しかし、その素子の微細化は現在、物理的な限界が見えてきており、新たな道筋を示す必要性が生じている。

その実現可能性を示すのがCMOS 2.0ということとなる。

(次回に続く)

本記事はimecの「The CMOS 2.0 Revolution」を許可を得て翻訳したものとなります

Julien Ryckaert(ジュリアン・リッカート)

Sri Samavedam(スリ・サマヴェダム)