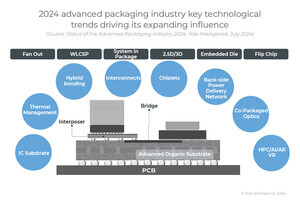

チップレットがムーアの法則に追いつくかどうかは、モノリシックSoCの機能と同様に、チップレットを1つのパッケージ内でどれだけ近くに配置して、チップレット間の高速で高帯域幅の電気接続を確保できるかに大きく依存している。

3Dシステム集積では、共通の基板(インターポーザーとも呼ばれる)を介してチップを並べて接続する2.5Dチップレット集積と、チップレットを3次元的に積み重ねる3D-SoCという2つの主要な業界の方向性が浮上している。

2.5Dインターポーザ技術

2.5D集積では、チップレットはシリコン、有機ポリマー、ガラス、またはラミネートの共通基板を介して接続される。imecは現在、シリコンと有機基板に注力している。シリコンインターポーザは、最も微細なピッチと優れた熱特性および電気特性を備えた高性能アプリケーション向けの確立された技術であるが、コストが高く、複雑でもある。そのため、代替として有機基板が研究され、最適化されている。

初期のチップレット集積では、ダイ間の相互接続にシリコンインターポーザ基板を使用することに重点が置かれていた。この集積では、2つの個別のチップレットを共通インターポーザ(接続を確立するマイクロメートルスケールの配線を備えた基板)上に近接して(50μmほど離して)配置する。シリコンインターポーザは、従来のBEOL Cu/酸化物ダマシンを利用して、μmおよびサブμmレベルの相互接続ピッチを高い歩留まりで実現している。

これは依然として有効なアプローチであるが、よりコスト効率の高いソリューションにつながる可能性があるため、代替技術への関心が高まっている。imecが提供するオプションの1つは、シリコン「ブリッジ」である。これは、チップレットをエッジのみで接続する小さなシリコンインターポーザーである

もう1つの代替案である超微細再配線層(RDL)相互接続技術では、シリコンを有機ポリマーに置き換え、チップレットを接続するための銅線の層を埋め込む。imecは現在この技術の最適化を図っており、シリコン対応製品と同様の相互接続密度の実現とシリコンとの互換性の向上に取り組んでいる。ピッチに関しては、インターポーザはサブミクロンピッチで依然としてトップの座を維持しているが、imecはRDLの2μmピッチ、さらに将来的にはサブミクロンピッチを目標としている。

シリコンインターポーザ技術の代替を模索するほか、imecは、追加機能を追加することでインターポーザをより価値の高いコンポーネントにする方法も研究している。たとえばインターポーザには、チップレットをノイズや電力異常から保護するための追加のデカップリングコンデンサーを搭載できる。

3D-SoC - ハイブリッドボンディングによりサブμmピッチを実現

高性能コンピューティングなどの一部のアプリケーションでは、高性能、より小型のフォームファクタ、またはより高度なシステム統合が求められるため、完全な3Dアプローチが好まれる場合がある。横方向の接続を確立する代わりに、チップレットを互いに積み重ねて3D-SoCを形成できる。このアプローチでは、追加のブロックは追加されないが、チップレットを一緒に共同設計し、同じチップであるかのように動作させることができる。ウェハツーウェハハイブリッドボンディングは、μm相互接続密度レベルで3D-SoCを集積するための重要なテクノロジである。これは、低温膨張係数を持つ2つのシリコンチップレットを接続することを意味している。このプロセスで重要なコンポーネントは、効果的な結合のために積層層の表面を平坦化して活性化し、スタック内の異なるチップレットを電気的に絶縁する誘電体である。imec独自のアプローチでは、結合誘電体としてSiCNを採用し、相互接続ピッチを700nmに縮小している。ロードマップでは、400nmや200nmのピッチも予測されている。

マイクロバンプとハイブリッドボンディング

2.5D技術では、電気的および機械的な接続を作成する小さなはんだバンプを使用して、チップレットがインターポーザ上に配置される。これらのマイクロバンプ間のピッチが細かいほど、接続が高速かつ安定する。業界でのマイクロバンプのピッチは通常50μmから30μmである。imecは、ピッチを10μm、さらには5μmまで減らす方法を研究している。

2.5Dで使用されるマイクロバンプと比較すると、3Dスタックのハイブリッドボンディングではピッチが大幅に小さくなる。では、ハイブリッドボンディングをあらゆる場所で使用できるだろうか?。確かに、ダイツーウェハアプローチ(シリコンベース)では、チップレットをシリコンインターポーザにボンディングして、ピッチを数μmにすることができる。ダイツーウェハの配置精度は現在、最高で250nmに近づいているが、最先端のウェハツーウェハボンディングでは、オーバーレイ精度が100nmまで低下する。ボンディング装置と関連プロセスの改善により、これらの数値はさらに50%減少すると予想されている。それでも、ハイブリッドボンディングには、表面活性化やアライメントなどの追加の処理手順が伴い、製造コストに影響を与える可能性がある。

ウェハツーウェハ接合、ダイツーウェハ接合、マイクロバンプは、コスト、ピッチ、互換性、相互運用性の間でトレードオフの関係にある。2.5Dでは、チップレットはさまざまなベンダーから提供されることが多く、一連のテストと操作をすでに受けています。マイクロバンプは、表面処理を必要としない標準化された方法を提供するため、好ましい選択肢となる。また、有機RDLの場合、有機ポリマーは加熱により膨張し、十分に平坦化できないため、マイクロバンプが依然として好まれる。

(次回に続く)

本記事はimecが同社Webサイトならびに「3D InCites」に寄稿した記事「Chiplet Interconnect Technology: Piecing Together the Next Generation of Chips (Part I)」を翻訳・改編したものとなります

エリック・ベイン(Eric Beyne)

ヘルト・ファン・デル・プラス(Geert Van der Plas)

エリック・ヤン・マリニッセン(Erik Jan Marinissen)