CCIX/Gen-Z/OpenCAPI

ところでCCIXとOpenCAPIの関係は? というと「よく似た別の物」という事になる。この辺りを比較した資料が丁度見つかったのでご紹介したい。

これはOFA(OpenFabrics Alliance)の13th Annual Workshop 2017における資料で、SpeakerはAMDのBrad Benton氏による"CCIX, Gen-Z, OpenCAP:Overview & Comparison"である。Gen-Zはこれまで紹介してこなかったが、2016年にスタートしたやはりOpen系のInterconnectである。CCIX/OpenCAPIとの最大の違いは、CCIX/OpenCAPIが主にシャーシ内か、せいぜいがシャーシ間の接続に留まるのに対し、Gen-Zは強いて言えばシャーシ間とかラック間の様な、もう少し長距離&接続台数の多いパートを担う事である。

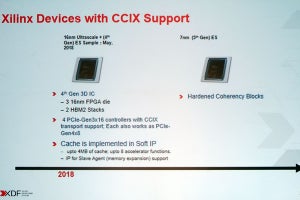

まずそれぞれのメンバー企業であるが、こんな具合(Photo13)。

すべての規格にAMD/Amphenol/ARM/IBM/Mellanox/Micron/Xilinxが加わっているという、ちょっと何が何だか状態になっているのがおかしい。ちなみにAmphenolはコネクタのベンダーである。あと、NVIDIAはこの時点ではOpenCAPIにしか参加していないが、Mellanoxを買収したことで結果的にすべての規格に参加したような形になっている。目立つのはここにIntelが全く参加していない事であるが、まぁそれは措いておくとして、それぞれの規格を簡単にまとめたのがこちら(Photo14~16)。

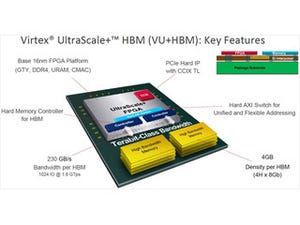

Gen-Zの基本的な考え方は、なんとなくIntelが2013年に提唱したRSA(Rack Scala Architecture)を彷彿させるものがあるが、基本的にはScale outなサーバにおける相互接続(ラック内のシャーシ間orラック間)をサポートするものとなっている。これに比べるとOpenCAPIはもっと限定的というか、CCIXのサブセットとでも言うような構成になっている。またOpenCAPI 3.0ではCache Coherencyは限定的(Accelerator側のCacheはサポートしない:Coherencyの対象となるメモリはあくまでHost側のもののみ)で、Full CoherencyとなるのはOpenCAPI 4.0からとなる。

それぞれのInterconnectの到達距離を示したのがこちら(Photo17)。

-

Photo17:SCMはStorage Class Memory。Local Memoryは今ならLocalのM.2とかNVDIMMおとか、Chassis SCMはU.2とかSATA/SAS SSD、Rack Pooled SCMはSSDベースのNAS/SANなどが相当する

Gen-Zが一番到達距離が長いのはRack to Rackの接続を考えているからで、それゆえIEEE 802.3(Ethernet)の、それもShort and Long Haul PHYをベースにしている。OpenCAPIは当初こそ独自であったが、4.0ではEthernetベースに近くなっている。CCIXのみがPCI ExpressのPHYをベース、という話である。

さて、この3つの規格を比較したのがこちら(Photo18)。これが一番わかりやすい気がするのだが、Gen-Zが一番帯域的には広いし到達距離も長いが、それはRack to RackのInterconnectだから当然であり、逆にCache Coherencyはサポート外なのでちょっと別枠であり、CCIXとOpenCAPIがかなり近い構成になっている。

ところでこの資料はOFAでのものなので、当然OpenFabricsとして使った場合、という議論で〆る事になる。OFAは基本的にはRDMA(Remote DMA)のSwitched Fabricを推進しているベンダーであり、元々はInfinityFabricをベースとしたOpenIB Allianceという団体が母体というかInfiniBand以外もサポートするように進化した結果として、複数のInterconnectの上でRDMAをサポートするといった話になっている。

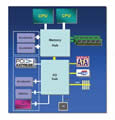

CCIXの場合、PCIeの延長という扱いになっており(Photo19)、利用可能ではあるのだが、範囲が限定されるとしている。

Gen-Zが一番OFAの希望とするところに近い(Photo20)が、色々足したいものはあるらしい。OpenCAPIもCCIXと似た感じ(Photo21)だが、CCIXよりさらに色々足すべきものがあるとする。

-

Photo20:問題はGen-Zのベンダーがこれを実装する予定があるかどうか、だろうか

-

Photo21:根本的な問題は、CCIXがAMDやArmベースSoCなど多数のホストが対応するのに対し、OpenCAPIは今のところIBMのPOWER9一択になることだろうか?

さて、まとめのページだが、面白いのはOpenCAPIとCCIXは技術的にはBridgingできそう、としており実際近い将来FPGAベースのBridgeが登場しそうとしている。これはどういう構成か? というと、NVIDIAのGPUをAMDあるいはArmベースSoCと組み合わせてシステム(ゲームならPCIeで十分なので、これはHPC/AI向けのサーバだろう)を構築する場合である。

近い将来の話で言うなら、NERSCに2020年から導入されるPerlmutterがまさにこれで、AMDのMilan(7nm+を使うEPYC)にNVIDIAのVolta-Next(次世代のVolta)を組み合わせたものである。System IntegratorはCrayであるが、具体的にどうMilanとVolta-Nextを組み合わせるのかは今のところ明らかになっていない。CrayのShasta Architectureも、さすがにNVLINKとCCIXの変換まではサポートしないと思うのだが、もしそうだとするとMilanのCCIXの先にFPGAベースのBridgeが挟まってNVLinkでVolta-Nextとつながる、なんて構成になっても不思議ではないだろう。

(次回は6月11日の掲載予定です)