Breakout session

さて、ここまでの説明についてはPDFがIntelのサイトより入手できるが、午後に行なわれたBreakout sessionはなぜかプレゼンテーションが未公開のままである。ということで、こちらから目に付いたものをかいつまんで幾つか紹介したい。

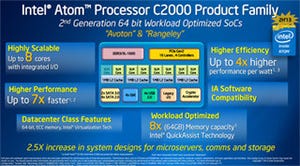

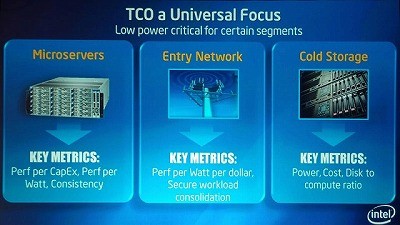

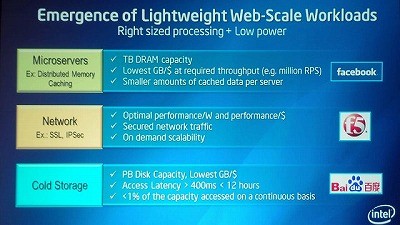

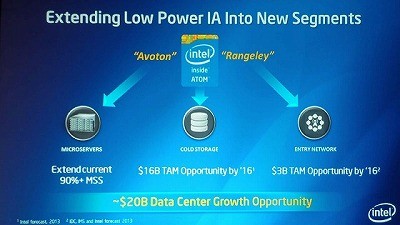

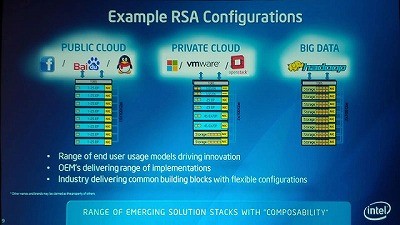

さて、まずはSDIの中で出てきたMicroServerやEntry Network、Cold Storageなど(Photo60)。それぞれに求められる特徴と具体的なターゲットをまとめたのがこちらである(Photo61)。こうした異なる要求に対して、ワークロードに最適化した形の構成を組める、というのがIntelの提案である(Photo62)。さて、こうしたマーケットにIntelがAvotonとRangeleyの2つの製品を投入するわけだが、両者は基本的に同じ(というか、断言はされなかったがおそらくシリコンレベルで同じ)であり、違いはNetwork処理のアクセラレータを持つか持たないか(というか、有効にするか否か)という事のようだ(Photo63)。

|

Photo60: このCold StorageにはTape Driveを組み合わせたJuke Boxも含まれるのかと聞いたら、流石にそれはないとの事。あくまでもRackに収まることが前提という話だった。 |

|

Photo61: Cold Storageのターゲットが百度というのは非常に興味深いが、アクセス時間は400ms以上でよい代わりに、とにかく安く大規模なストレージ、というのはこれまで存在しなかったのは事実だ。 |

|

Photo63: Cold Storage向けにはRAID用のXORエンジンも、という気もしなくはないのだが、Photo21でわかる通りAvoton/RangeleyのどちらもSATAは合計6ポートしかない。 |

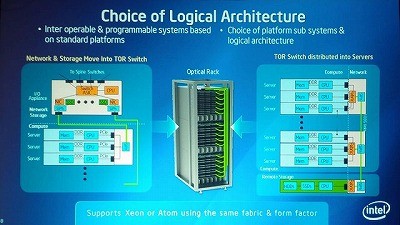

次がSiPh対応の"Optical Rack"の話。先ほどは概念図が出されたが、こちにはもう少し詳細な話が出ている(Photo64)。ラック最上段にはSiPhをSwitch ASICを組み合わせたBackPlane(左側上段)が入り、Xeon 2P×3のトレイは左側下段、Avoton(かRangeley)×30のトレイは右側のような構成になるようだ。

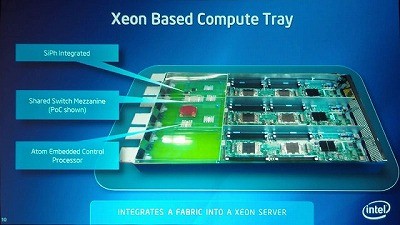

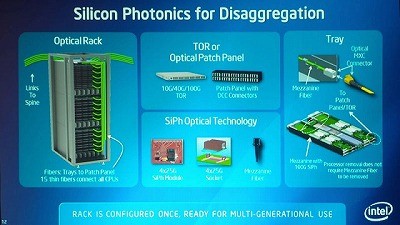

では具体的にこれを使う事でどんな形にWorkload Optimizationが可能なのか、というのがこちら(Photo65)。で、先ほどPhoto20に出てきたXeon 2P×3のトレイだが、Xeonの奥のメカニカルモックアップ部の説明がこちら。3枚のXeon 2Pマシンを簡単なFabricで繋ぎ、そこからSiPhが出る構造になっているのが判る。これを構成するための要素技術がこちらである(Photo67)。肝になるのは、現在のEthernetと同じように簡単にPatch Panelを使って接続を自由に変えられること、それとSiPhが非常に安価に利用できる構造になっていることだろう。

|

Photo65: よく見ると判るが、何故かここではXeon EN/EP/EXを使う事になっていて、Atomがない不思議。ちなみにPrivate Cloud向けでは100Gbpsの帯域では足りないためか、100GbpsのSiPhを二重化している。 |

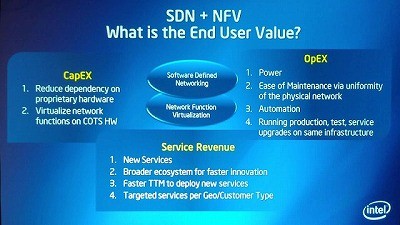

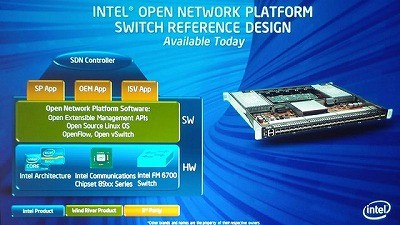

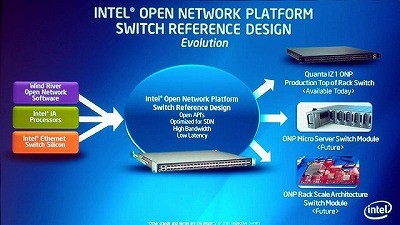

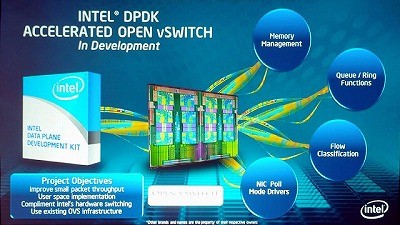

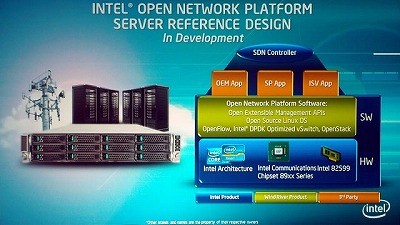

さて、ここからはソフトウェアの話。先ほどから何故かネットワークアプライアンスがちらちら出てきた事にお気づきの読者も多かろうと思うが、端的に言えばIntelはこうしたアプライアンスを全部Intelベースの汎用品で置き換えるという壮大な構想を今回発表した(Photo68)。具体的に言えば、汎用のハードウェア構成を生かして構築できるSwitch(Photo69,70)であり、既にQuantaがこれを利用したQuanta IZ1(T3048-IZ1)というSDN対応Switchをリリースしていることも明らかにされた。また汎用のハードウェアを使う、Intel DPDK(Data Plane Development Kit)も現在準備されており、これによりOpen vSwitchを簡単に構築可能という話も発表された(Photo71)。更に上位層として、Intel Open Network Platform Server Reference Designも現在開発中とされた(Photo72)。

次ページ:まとめて解説など