今年5月に開催されたPCI-SIG Developers Conferenceの席上、PCI-SIGのChairmanであるAl Yanes氏曰く「Geneseo、これはあくまでもIBMとIntelがそう呼んでいるだけで、正確にはPCI Express Extensionとなるが、これに関しては何も決まっていない」とされたGeneseoだが、その後の進展は著しかったようだ。まずはこのあたりから説明したい。

PCI Express Protocol Extension

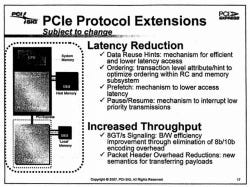

こちらの電話インタビュー時には詳細が発表されなかったPCI Express Protocol Extensionだが、今回その一端が明らかにされた。まずLatency Reductionとして示された(Photo01)のは、Data Reuse Hints/Ordering/Prefetch/Pause&Resumeという機能の追加である。

|

|

Photo01:これと次のPhoto02は、PCI-SIGのAl Yanes氏との1to1 Meetingの際に示されたもの。Incresed Throughputは確かにプロトコルに関係はあるが、これはGen3のBase Specificationで実現されている内容なので、Extentionには入らないと思うためここでは割愛する。 |

Data Reuse Hintsは、Root Complexが持つキャッシュを再利用するための仕組みである。これまでRoot Complexがローカルキャッシュを持つという話はなかった。勿論持っても問題はないのだが、そうした実装を聞いた例はない。にも関わらずこうした話が出てくるのは、Gen3ともなるとRoot Complexもメモリアクセスだけでは間に合わなくなり、ローカルキャッシュを持つ可能性が高く、これを利用するためにHintを追加するということだろう。プロセッサと異なり、Root Complexが自発的に処理をする訳ではないから、普通にキャッシュを持ってもあまり効果的ではない。なので、デバイスからのアクセス時にHint情報を付加することで、メモリに格納しても間に合う程度の頻度のものか、ローカルキャッシュに格納したほうが効果的なほどの頻度でアクセスされるかが判るという訳だ。

Orderingは、メモリとRoot Complexの間の転送に関してアクセス順序を明示的に指定するというものだ。これはあくまでRoot Complexの機能だが、次のPrefetchは、デバイスが(Root Complexに接続される)System Memoryをアクセスする際の高速化を図るものだ。例えばRoot Complex→Deviceへの転送時にPrefetchを掛ける事で、メモリ読み出し時のレイテンシを最小化できる。

最後のPause/Resumeは、InterruptにPriorityをつけるためのメカニズムと言っても良い。より優先度の高いInterruptを先に処理できるようにするためのもので、あるInterruptの処理中に、それをPause(退避)/Resume(復帰)させるための仕組みだ。これにより、特定の処理に必要なLatencyを削減することができる。

面白いのはこのPause/Resume、各々のVirtual Channel毎に管理できることだ。本来デバイス毎の帯域の調整はVirtual Channelの帯域を制御することで行えるから、ある程度のPriority管理はここでも擬似的に可能だが、Pause/Resumeはこれを補強するというわけではなく、VC経由で各デバイス毎にPause/Resumeの管理が可能ということになる。これはどちらかというと、IOV(I/O Virtualization)を前提にしているようだ。