UNIVACのLARC

米国の水爆の父として知られるカリフォルニア大学のRadiation Laboratory(後のLawrence Livermore National Laboratory:LLNL)のEdward Teller博士が、1955年に、IBMとUNIVACにスーパーコンピュータの開発提案を要請した。

IBMの提案は、性能は高いものの、納期が1年遅く、費用も100万ドル高いということで、UNIVACが契約を獲得した。このスーパーコンピュータは「Livermore Advanced Research Computer(LARC)」と呼ばれる。

UNIVACは1960年6月にこのコンピュータを完成しLivermoreに納入された。

LARCの全景は、図1.13のようになっており、4つの20ft×4ft×7ftのキャビネットで構成されるコンピュータ本体に磁気ドラム、磁気テープ、プリンタ、コンソールなどが接続されている。前述のENIACから14年で、ずいぶん、あか抜けた外観になっている。

-

図1.13 UNIVAC LARCシステムの全体構成。基本構成は4本の大型ラックに収容され、磁気ドラム、磁気テープ、プリンタなどとコンソールが接続されている (出典:UNIVAC-LARC General description)

LARCの4つのキャビネットの内の1つはI/OプロセサやDMA、1つは演算プロセサ、残りの2つのキャビネットはメモリである。

今日のPCなどとは異なり、LARCは計算処理を行うプロセサ(コンピュータと呼ぶ)とI/O処理を行うプロセサ(プロセサと呼ぶ)を持つヘテロジニアスマルチプロセサ システムとなっている。これはI/Oの処理をオフロードして演算プロセサの性能をフルに発揮させるためで、現在でもメインフレームなどでは一般的な構成である。また、2017年時点のTop500 1位である中国の太湖之光スパコンは、64個のスリムな計算コアに、1個の大型のOSを走らせるコアを装備しており、この大型コアで通信や、I/Oの処理を行っている。このように、今日の超並列のスパコンでもI/O専用のプロセサコアを持つものが多くなってきている。

LARCは語長が48bitのマシンで、命令、データともに48bitで、10進12桁の数値を処理するマシンであった。数値データは4bitで10進1桁を表し、整数は符号ディジット+10進11桁。浮動小数点数は、符号ディジット+指数2桁+仮数9桁という表現になっている。なお、数値については2語を使う倍精度の形式もサポートしているが、12ディジットの最初のディジットは符号で無ければならないという制約があり、整数は10進22桁、浮動小数点数の仮数は20桁となっている。

メモリはエラーチェック機能を持ち、4ビットデータにパリティチェックが付けられ、物理的には1語60bitとなっていた。メモリは1バンク2500語で、1キャビネットに4バンクを収容しており、最大39バンクまで拡張可能であるが、図1.13の構成では8バンクで、メモリ容量は20,000語であった。

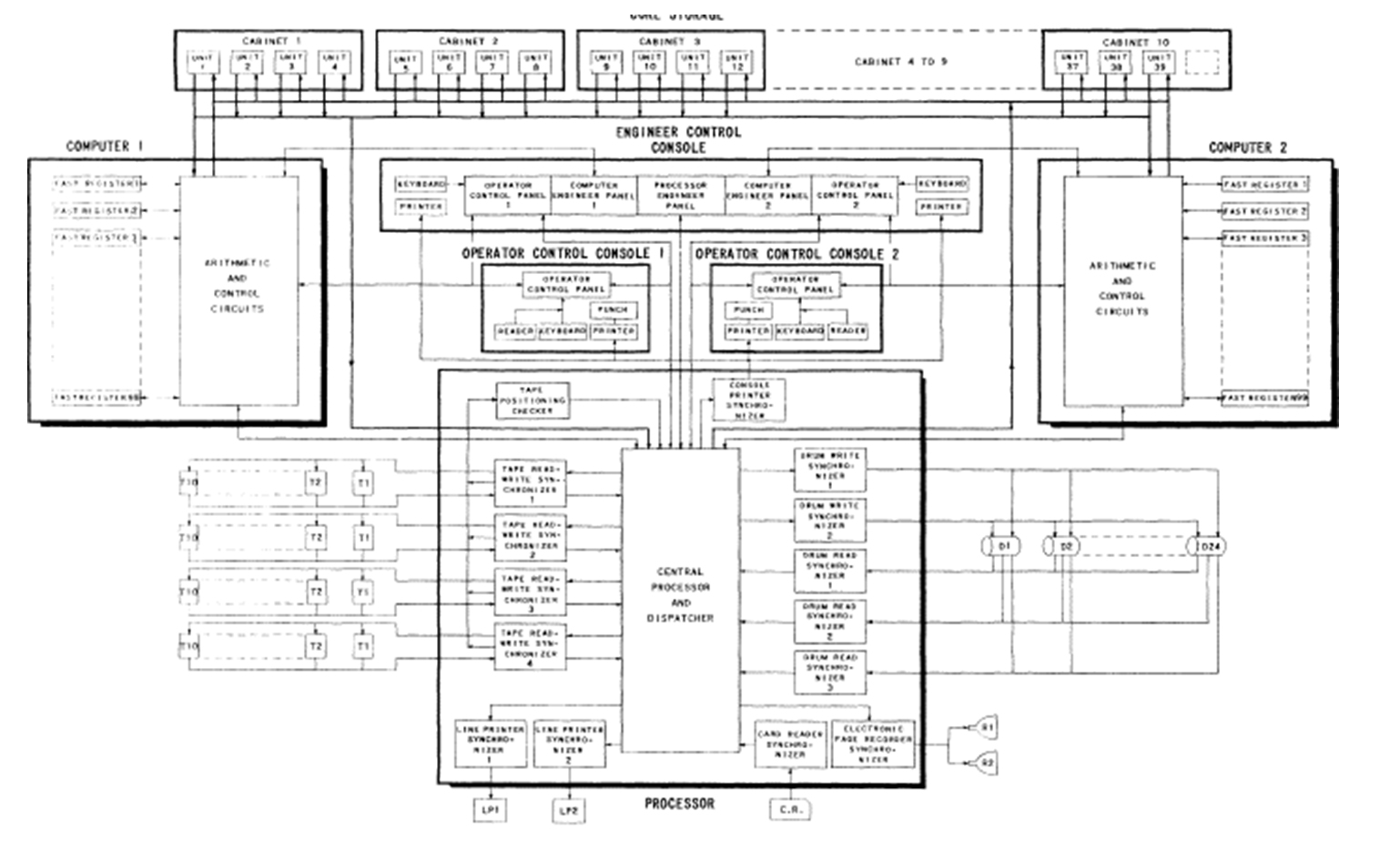

LARCの構成を図1.14に示す。このメモリには計算プロセサ、I/Oプロセサとシンクロナイザと呼ぶ、I/OコントローラやDMAに相当するユニットが接続され、LARCシステム全体の記憶と通信を担っている。

-

図1.14 LARCのシステム構成。最大39バンクのコアメモリ、2台の計算プロセサ、1台のI/Oプロセサ、4台のテープシンクロナイザ、5台のドラムシンクロナイザ、合計4台のプリンタなどのシンクロナイザを持つ

メモリのサイクルタイムは8μsであるが、2つのメモリバンクを並列に使い4μsごとに新しいアクセスができるようになっていた。

LARCのバスサイクルは4μsで、これを8つのサブサイクルに分割して、各サブサイクルに、

- I/Oプロセサ 命令、データ

- 演算プロセサ(コンピュータ)1 命令

- 演算プロセサ(コンピュータ)2 データ

- I/Oコントローラ (シンクロナイザ)

- 未使用

- 演算プロセサ(コンピュータ)2 命令

- 演算プロセサ(コンピュータ)1 データ

- I/Oコントローラ (シンクロナイザ)

がバスを使用するという構造であった。このように、LARCはコンピュータ1と2を持つことができるアーキテクチャであったが、製造されたLARCは2台だけで、どちらもコンピュータ1だけの構成のもので、デュアル計算プロセサのマシンは作られなかった。

LARCはPhilco社が開発したサーフェスバリア型というバイポーラトランジスタを使う初期のトラジスタコンピュータであり、前世代の真空管式のコンピュータと比べて、大幅な小型、低電力化がなされていた。

LARCの演算プロセサはパイプライン制御となっており、単精度の加減算は、整数でも浮動小数点数でも4μsごとに実行することができた。これは250KFlopsのピーク演算性能である。1954年に作られた真空管式のIBM 704のピーク性能は12KFlopsであるので、LARCは20倍強の性能を持つスーパーコンピュータであった。

LARCの計算プロセサは、メモリにマップされた26個の汎用レジスタ(最大99レジスタまで拡張可能)を持ち、アクセス時間は4μsであるが、使用頻度の高いアキュムレータとインデックスレジスタは1μsでアクセスできる高速のコアメモリで作られていた。

LARCは、浮動小数点数の加算は4μs、乗算は8μs、除算は28μsで実行することができた。また、2つの語を繋いで使う倍精度形式がサポートされており、倍精度の浮動小数点数の加算は16μs、乗算は36μs、除算は168μsであった。この時間は、演算時間だけではなく、メモリアクセスも含んだ処理時間である。

I/Oプロセサは、プログラマブルな汎用プロセサであるが、整数の加算が8μsで、乗除算はサポートされていないなど、計算プロセサと比較すると演算機能は簡易な構造になっている。一方、現在のI/Oコントローラに相当するシンクロナイザからの動作完了などの通信を受け取って、次の動作を開始させるなどの機能は充実していた。I/Oプロセサは汎用のプロセサであるので、磁気ドラムや磁気テープ、プリンタなどを制御するだけでなく、データのソートやマージなどを行わせることができた。 なお、LARCは25万語の磁気ドラムを12台装備しており、当時としては大容量のストレージを持っていた。

面白いのはElectronic Page Recorderという装置で、毎秒15,000字の文字や毎秒2,000点のグラフを出力することが出来る超高速の出力装置である。文字もグラフも出力できるということから推定できるが、CRT(ブラウン管)に表示して、それを高速の35mmカメラで撮影するという仕掛けになっていた。当然、銀塩フィルムへの記録であり、ランニングコストは高かったと思われる。

LARCが、それ以前の、真空管を使ったIBM 704などと比べて圧倒的に速いスピードを実現できたのは、トランジスタのお陰である。トランジスタは真空管よりもサイズが小さく、ずっと低い電圧で動作し、消費電力が小さいので、多数のトランジスタを高密度で実装することができた。多数のトランジスタを使ってパイプライン処理を行い、より高速の演算器を作ることができた。

また、磁気コアメモリが実用化され、大容量で比較的高速な記憶装置が使えるようになってことも性能向上の大きな要因である。

(次回は1月26日に掲載します)