A64FXのエラー訂正機能

スパコンは規模が大きく、どこが故障しても実行中の計算に影響を及ぼす。このため、エラーの発生を見逃さないこと、可能な限りハードウェアのエラーを訂正することが重要である。

このため、A64FXプロセサは、メインフレームクラスのハードウェアによるRAS(Reliability、Availability、Serviceability)機能を備えている。具体的には、すべてのキャッシュはECCによるエラー訂正か2重化によるエラー訂正機能を備えている。また、実行ユニットにはパリティチェックを施し、演算器のエラーも検出している。

そして、パリティチェックだけではエラーは訂正できないが、A64FXでは、パリティエラーが検出された場合には、その命令の実行をやり直して訂正を試みる。トランジスタが壊れてしまったような場合は、やり直しても同じエラーになってしまうが、宇宙線などに起因する一過性のエラーの場合は、やり直しでエラーを訂正することができる。このために、A64FXチップは約12万8400個のエラーチェッカを組み込んでいる。

また、Tofuインタコネクトも伝送エラーを検出して、ハードウェアでエラー訂正を行う機能を備えている。

次の図の右側の図は、チップのプロット図を色分けしてエラー検出関係の機能レベルを示したもので、緑の部分は1bitエラーを訂正できる部分、黄色の部分は1bitエラーが検出でき、再実行で訂正を試みる部分、灰色の部分は、回路が作られていないなどで、エラーが起こっても問題にならない部分を示している。

-

A64FXプロセサはECCによるエラー訂正やパリティチェックでエラーを検出し、エラーを起こした命令の再実行で訂正を行う機能を持っている。右下のチップの図の緑の部分は1bitエラーが訂正できる部分、黄色は再実行でエラー訂正をトライする部分、灰色はエラーが問題にならない部分を示す

ArmのHPCエコシステムに貢献するソフトウェアスタック開発

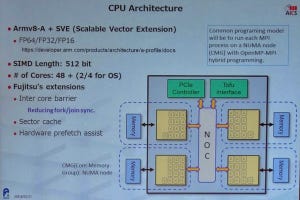

ソフトウェアに関しては、理研と富士通はPost-Kスパコンのソフトウェアスタックの開発を行っている。富士通担当のコンパイラは、SVEとHBM2を使うA64FXの性能を最大限引き出せるように最適されている。富士通は、理研を始め、Linaro、OSSコミュニティ、関係ISVなどと協力して開発を行っており、ArmのHPCエコシステムに貢献している。

OSはアシスタントコアで動かすLinuxと計算ノードで動かす軽量のMcKernelの開発を行っており、McKernelは理研の担当である。プログラミング環境は、理研が開発する並列プログラミング用のXcalableMP、ノード間通信を行うMPI、汎用の並列プログラミング環境であるOpenMP、COARRAY、数値ライブラリなどを開発する。コンパイラはC、C++、Fortranを用意する。当然、デバグ環境や性能チューニングツールも用意される。

さらにシステムマネジメントソフトウェアやファイルシステムも開発を行う。

-

ソフトウェア開発は、富士通と理研が中心になり、LinaroやOSSコミュニティなどと協力して開発する。そして、ArmのHPCエコシステムにも貢献していく。OSはアシスタントコアで動かすLinuxと計算コアで動かす軽量のMcKernelを開発する

ポスト「京」スパコンはどの程度の性能なのか

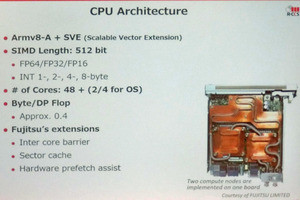

まとめであるが、A64FXは、Arm v8 SVAアーキテクチャに準拠する世界初のプロセサであり、日本の次期フラグシップシップスパコンであるPost-Kの計算エンジンとして使用される。Armアーキテクチャのプロセサであるが、中身はArmMの設計ではなく、富士通の蓄積したマイクロアーキテクチャを使って、HPCやAIに高い性能を実現しているという。

現在は、Post-Kスパコンだけの使用であるが、Armアーキテクチャの採用は一過性のものではなく、富士通はパートナーと協力して活動し、Armのエコシステムに貢献を続ける。また、Armアーキテクチャのプロセサの開発も継続して行っていく。

-

A64FXは、Arm v8 SVAアーキテクチャの世界初のプロセサであり、日本のポスト「京」スパコンに使用される。富士通の蓄積したマイクロアーキテクチャを使って、HPCやAIに高い性能を実現している。富士通はパートナーと協力して活動し、Armのエコシステムに貢献を続ける。また、Armアーキテクチャのプロセサの開発を継続して行う

今回の発表では、A64FXプロセサの演算性能はFP64では2.7TFlops超と発表されたが、システム全体で何個のA64FXプロセサが使われ、システム全体の規模がどの程度になるのかは明らかにされなかった。

現在の富士通のFX100スパコンは1TFlops/ノードであり、100,000ノードで100PFlopsとなっている。FX100はラック当たり216ノードを収容できるので、100PFlopsのシステムは463ラックを必要とする。

京コンピュータは800ラックあまりを使っており、FX100であれば200PFlops程度のスパコンとなる。これにSPARC64 XIfxからA64FXへの性能アップが3倍とするとPost-Kスパコンのピーク演算性能は600PFlops程度と見積もられるが、これは筆者の勝手な想像である。

それから、2018年6月にフランクフルトで開かれたISC 2018での発表では、Post-Kプロセサの試作チップをパワーオンしたと発表していたが、今回の発表では「試作チップ」という言葉は無くなっていた。

理研の発表しているタイムテーブルは、幅があるのであるが、Post-Kスパコンは2021年の第3四半期からの運用開始となっている。このスケジュールであれば、CPUチップの開発には、まだ、1.5年~2年くらいの余裕があると思われ、5nmプロセスが順調に立ち上がれば、5nmプロセスで作り直すことも可能ではないかと思われる。しかし、「試作」という表現が消えたことは、現在のチップは問題なく動いており、7nmプロセスのままでも実用になると判断したのではないかと思われる。

もし、そうであるとすれば、ハードウェアの開発工程としては余裕ができ、運用開始時期が早まるという可能性も出てくるのではないかと思われる。前倒しができれば、日本のスパコンのレベルアップが早まり、競争力の強化につながり、望ましいことである。