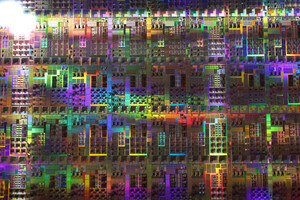

imec主導の欧州連合(EU)の取り組みである「NanoICプロジェクト」が、新たにプロセス設計キット(PDK)として、ファインピッチ再配線層(Redistribution Layer;RDL)PDKとダイ・トゥ・ウェハ(D2W)ハイブリッドボンディングPDKを発表した。

NanoICプロジェクトは、imecの300mmクリーンルームを活用する形で欧州での2nm以降の半導体試作を実現することで、欧州勢の先端半導体でのイノべーションの加速を目指す取り組み。今回のPDKの提供は、欧州の大学やスタートアップ、業界イノベータなどが先端パッケージングの実現を容易にする重要な要素となるとimecは説明している。

今回の2つのPDKは、高密度チップ間統合の検討に必要な設計ルールと検証済みのビルディングブロックへの早期アクセスを設計者に提供するもので、ファインピッチ再配線層PDKでは、ポリマーベースの基板を用いて高密度チップ間接続を実現する新たな手法が導入された。従来、そうした基板は微細配線に対応できず、高度なパッケージングへの適用が制限されていたが、imecの研究開発の成果としてポリマーベースのRDLにおいて微細な配線が可能となり、その結果、現在の主要な商用ファブが提供する機能を超える性能を提供できるようになったという。

具体的には線幅と線間隔は1.3μmまで、マイクロバンプピッチは20μmまで対応しており、UCIe-Advanced Die-to-dieインタフェースにおいて、通信速度を最大40%向上させ、ビットあたりの消費電力を最大15%削減できるインターコネクトを実現できるとする。

一方のD2WハイブリッドボンディングPDKは、3次元構造を活用してダイ間をコンパクトに直接接続することを可能とするもの。従来の銅バンプの代わりに、ダイとパッケージインタフェース間に酸化膜同士の直接接続を形成することで、銅バンプに伴う寄生成分を排除し、低損失でエネルギー効率の高い通信経路を実現することを可能にするという。

完全なテープアウト機能に向けた重要な一歩

提供が開始された最初のバージョンでは、設計者が技術の評価をするために必要なツールとして、体系的なレイアウト作成、自動配線とカスタム配線、設計ルールチェックなどが提供されている。imecでは、これをパスファインディングPDKと位置付けており、今後のバージョンアップにより、テープアウト機能につれて、テープアウト機能を備えた完全な製造対応ツールセットへと進化していくとしており、設計者がそれらのPDKで作成したレイアウトをパイロットラインで製造し、実際にシリコン上でコンセプトを検証できるようにしていくとしている。

なお、NanoICの公開済みPDKは、N2(2nmプロセス)、A14(1.4nmプロセス)、eDRAMの既存PDKに今回の2つのPDKが加わり5種類まで拡大したことになる。これにより対応範囲がロジック、メモリ、そしてインターコネクトまで拡大されたこととなる。

開発に協力するimecは、これまで次世代ロジックデバイス向け先端プロセス技術の開発に注力してきたが、一連のPDKが出そろったことで、これからはIBM同様、次世代の高密度LSIの開発に取り組むとともに、開発・試作ファウンドリサービスを提供する組織へと進化することになる。