3D ICの設計にソシオネクストが対応

ソシオネクストは8月28日、3D ICに対する設計を拡充し、チップレット、2.5D、3Dおよび5.5Dを含むパッケージング技術のラインナップとSoC設計能力を活かした高性能・高品質なソリューションを提供できる体制を整備したことを発表した。

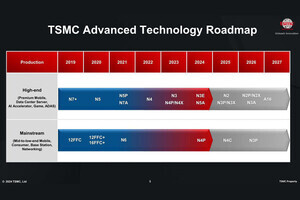

TSMCのSoIC-Xを活用して実現

具体的には、TSMCの3D積層技術「SoIC-X」を活用したパッケージデバイスのテープアウトを完了したという。このデバイスではTSMCのN3(3nmプロセス)を活用したコンピュートダイとN5(5nmプロセス)を採用したI/OダイをFace-to-face(F2F)構成で組み合わせることで、相互接続距離を最小化し、従来の2Dおよび2.5Dと比較して信号遅延と消費電力の削減を可能にするとしている。

ソシオネクストでは、ダイを垂直に積層する3D ICの開発について、これまでの2.5Dで培った経験と実績ある手法を活用していくとしており、それにより3nmや5nmといった異なるテクノロジーノードと、各ダイごとに分けられたロジック、メモリ、インタフェースといった機能を1パッケージに統合し、パフォーマンスと密度、コスト面での最適ソリューションの提供を図るとする。

また、垂直方向に積層することで、より小面積で多機能の実装が可能になることから、従来、先端パッケージが活用されてきたAIやHPCのみならず、スペースに制約のあるコンシューマ分野での活用も期待できるようになるとするほか、ダイとダイの接続をより短く、かつ広げることができるため、低遅延化および広帯域化につなげることもできるようになるともする。さらに、コンパクトなインターコネクトの導入により、インピーダンスを低減でき、消費電力の削減にもつながることが期待できるともしている。

なお、ソシオネクストでは、今回の3D ICへの対応について、ヘテロジニアスインテグレーションの推進に注力していることを示すものであると説明している。