半導体集積回路の分野で最大級の国際会議である「ISSCC 2025」が2月16~20日、米カリフォルニア州サンフランシスコで、「The Silicon Engine Driving The AI Revolution(AI革命を主導するシリコンエンジン)」を開催テーマに開催される。

基調講演は4件が予定されており、登壇者はIntel SVPのNavid Shahriari氏、マサチューセッツ工科大学 教授のDaniela Rus氏、Samsung Electronics Corporate PresidentのJung-Bae Lee氏、Infineon Technologiesのオートモーティブ事業部プレジデント兼CEOのPeter Schiefer氏である。Intelは当初、Pat Gelsinger CEO(当時)が登壇すると予告されていたが、2024年12月の退任に伴い、Shahriari氏に変更となった。いずれも開催テーマに沿ったAI関連の講演が予定されている。

パネル討論は、「量子コンピューティング:どこの量子ビットが優れているか?」「次世代AI:障壁、チャンス、方向は?」「アナログ回路設計:まだ魅力的・それともデジタルにとってかわられる?」の3テーマが取りあげられる。チュートリアル・セッションでは、Samsung Electronicsによる「DRAM I/Oの基礎」はじめ10件の講義が行われる。

投稿論文数が900件を突破も採択論文数は246件で採択率は27%

ISSCC 2025の論文投稿数は914件と、前回(ISSCC 2024)から4.7%(41件)増加し過去最高となった。2024年も、従来の600件前後から、一気に873件へと増加したが、今回はさらに増加する結果となった。また、採択数は前回から12本増の246本となったが採択率は前回とほぼ同じ26.9%で、相変わらずの狭き門となっている。

採択数を地域(大陸)別に見ると、極東(FE=アジア)が165件と最も多く、全体の3分の2以上を占めている。アジアの採択数は前回から17件増加したのに対し、北米は7件、欧州は2件減少した。国/地域別に見ると、前回に続いて中国(香港/マカオ含む)が大学を中心に採択数を伸ばして最多の92件とし、米国(55件)、韓国(44件)に差をつけた。北京大学およびマカオ大学の採択件数がそれぞれ15件とするほか、清華大学も13件と多く、このほか韓国のKAISTが10件採択されている。

いずれの地域でも採択論文は大学からのものが増加傾向にあり、ISSCC 2025では、大学:企業:研究機関の比率は79:19:2となった。新たな半導体回路設計は 以前のような企業ではなく、大学が中心になってきている。中国は投稿数が多いだけでなく、レベルも高くなっており、採択率も年々向上している点が注目されるが、これは最近のVLSI SymposiumやIEDMにも共通した傾向である。

日本からの論文採択数は8件

ISSCC 2025における日本からの論文採択数は8件で、ISSCC 2024と比べて3件減少している。採択されたのは、東京大学、東京科学大学(旧東京工業大学)、キオクシアがそれぞれ2件、ソニーセミコンダクタソリューションズと大阪大学がそれぞれ1件ずつとなっている。他国からの発表論文の中に、日本勢であるブリルニクス、慶應義塾大学、TSMCデザインテクノロジージャパンが共著者として含まれているものがあるが、分類は筆頭著者の所属国で行われるため日本からの論文としてはカウントされない。また、2024年には2件採択されていたルネサス エレクトロニクスの採択もなかった。

企業別の採択件数トップはSamsung Electronicsの12件、2位はMediaTekの7件、3位はIntelとTSMCの各6件となっている。

メモリ分野でキオクシアとSK hynixが共同研究成果を発表

メモリ・セッションでは、キオクシアが2件の発表を行う。1件はWestern Digitalとの共著で、332層の3ビット/セルの1Tビット3次元NANDフラッシュメモリで29Gビット/mm2と4.8Gビット/秒/ピンのI/O速度を実現したもの。もう1件はSK hynixとの共著で、64Gビットの大容量MRAMである。キオクシアは、以前からSK hynixと研究協業を行っている。SK hynixは単独で独自の4ビット/セルによる2Tビット3次元NANDフラッシュメモリを発表する。

Samsung Electronicsは400層を超える3ビット/セルの1Tビット3次元NANDフラッシュメモリ、データレートが42.5Gビット/秒と高い24GビットGDDR7 DRAMなどを発表する。また、TSMCとIntelはGAA(Gate All Around)FETを採用したSRAMを発表する。TSMCのSRAMは2nmプロセスで製造し、ビット密度は38.1Mビット/mm2、IntelのSRAMは「Intel 18A」プロセスで製造し、ビット密度は34.3Mビット/mm2であるという。

Intel、AMD、IBMが新型プロセッサ発表

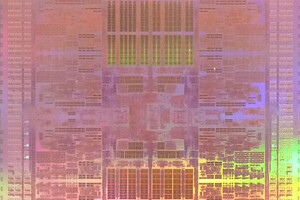

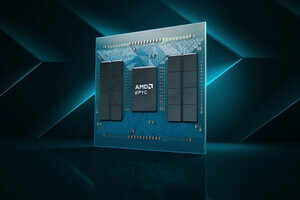

プロセッサ・セッションでは、Intelが、「Intel4」プロセスで製造された、「Granite Rapids-D」(開発コード名)のMPUを発表する。既存のXeon Dの次世代製品である。IBMはSamsungの5nmプロセスで製作されたメインフレーム「Z」向け次期MPU「Telum II」を発表する。最大5.5GHzで動作し、最大768TOPSの8ビット整数演算性能を持つ。AMDは、最新の64ビットCPUコア「Zen 5」(開発コード名:Turin)を発表する。これは、TSMCの4nm FinFETプロセスで製造され、ノートPC向けMPU「Ryzen AI 300シリーズ」やデスクトップPC向けMPU「Ryzen 9000シリーズ」、サーバ向けMPU「第5世代EPYC」に採用されるという。このほか、MediaTekは、3nmプロセスで製作された0.168mm2と小型のNPUを発表する。

通信分野では、日本の大学の論文が3件採択されている。東京科学大学は256エレメントのKaバンド向けフェーズド・アレー・レシーバーと、CORDIC(COordinate Rotation DIgital Computer)を使わない高電力効率のデジタル・ポーラー・トランスミッターを発表する。東京大学は、量子化雑音除去に向けた5.7GHzのフラクショナルN型PLLを発表する。

アナログ分野は、Samsungが効率98%の50W無線充電器と2入力で双方向の3レベル電池充電器を、Intelが3nm FinFETプロセスを用いたマルチフェーズ電圧レギュレーターを発表する

MediaTekは4nm FinFETプロセスによる12ビットのタイムインターリーブA/D変換器(0.43mm2のチップ面積で、変換速度は16Gサンプル/秒)、Analog Devices(ADI)は16個のタイムインターリーブ9ビット逐次比較型A/D変換器(160mWの消費電力で12Gサンプル/秒の変換速度)を発表する。TSMCは3nm FinFETプロセスによるCMOSベースの参照電圧を発表する(論文番号:4.6)。リップルが非常に少ない参照電圧を発表する。

ソニーやSamsungがグローバルシャッター式CMOSイメージセンサを発表

イメージセンサ分野では、ソニーセミコンダクタソリューションズが、25.2M画素のフルフレームのグローバルシャッター式CMOSイメージセンサを発表する。全画素にA/D変換器が付く2層積層型で、120フレーム/秒で全画素を同時に出力できるという。

Samsungは、50M画素のローリングシャッター式でも12.5M画素のグローバルシャッター式でも動作が可能な、モバイル機器向け3層積層型のCMOSイメージセンサを発表する。

Metaは3層積層型で400×400画素のCMOSイメージセンサ、SolidVueは160×90画素のフラッシュLiDAR(Light Detection And Ranging)を発表する。

このほか、革新的トピック分野では、大阪大学が、16チャネルのマルチモーダル・ガスセンサを、東京大学はビアプロブラム方式のDNN(Deep Neural Network)処理プロセッサを発表する。

なお、ISSCC 2025では、対面(in-person)参加の登録のほか, 後日ビデオ視聴(on-demand)するための登録が可能である。ただし、イブニングセッション(パネル討論)やデモセッション(回路の動作実演)など一部のセッションはビデオ視聴できない点に注意が必要である。