半導体および電子デバイスに関する世界最大級の国際学会「IEDM 2024」が2024年12月7~11日にかけて、米サンフランシスコ市にて開催されたが、その基調講演にTSMCの上席副社長(EVP) 兼 共同最高執行責任者(COO)のY.J. Mii氏が登壇。「半導体産業の展望と新しい先端技術」と題して、半導体産業の展望を語った。

同氏は、講演の冒頭、「半導体業界は、新しい材料、高度な処理技術、最先端の設計が融合してテクノロジーの未来を形作る、イノベーションのダイナミックな産業分野である。テクノロジーのスケーリング(比例縮小)の原則に支えられたこの分野は、限界を押し広げ続けており、AI(人工知能)、HPC(高性能コンピューティング)、5G/6G、自動運転、IoTなどの革新的なアプリケーションを可能にしている。時間の経過とともにスケーリングが進化し、チップの効率とパフォーマンスの新たなレベルが実現している。地平線は、EUVリソグラフィのブレークスルー、CFET(コンプリメンタリFET)などの新しいデバイスアーキテクチャ、新しい低次元チャネル材料、DTCO(設計・プロセス技術の同時最適化)の戦略的相乗効果で明るく輝き、刺激的な新しいテクノロジー時代への道が開かれようとしている。さらに高度なパッケージング技術によりシステムレベルのパフォーマンスが向上し、計算能力が融合されて現在の限界を超えるようになるだろう」と述べ、半導体業界の先行きは明るいとの見方を示した。

また、「RF、不揮発性メモリ、電源管理、CMOSイメージセンサ、シリコンフォトニクスなどの成長により、革新的なデバイスの範囲が拡大している」とスペシャルティテクノロジ(特殊技術)の重要性にも言及するなど、半導体業界の新たなトレンドの探索と、これらの先端分野がどのようにスマートテクノロジーの統合を推進し、社会に明るい未来もたらすかの洞察が語られた。

2030年の半導体市場のけん引役は何か?

同氏によると、半導体産業は1980年以降、PC、インターネット、スマートフォン(スマホ)、クラウド、AIなどといった巨大な市場を形成するアプリケーションが次々と現れることで市場規模を拡大させてきており、2030年にその市場規模は1兆ドルに達する見込みとされている。

その2030年における半導体市場のプラットフォーム別売上高比率はHPCが40%でトップ、次いでモバイルが30%、オートモーティブが15%、IoTが10%、その他5%と予想されるという。

仮に2030年に半導体市場の規模が1兆ドルに成長すると、それを搭載する電子産業の市場規模は3兆ドルに、IT産業の市場規模は12兆ドル規模に、そして世界のGOPは145兆ドル規模に成長することが期待されるとする。

AIがあらゆる製品で活用される時代に

AIの普及は留まるところを知らず、今後、PC、スマホ、データセンター、ADAS、ロボットなど、あらゆる製品やアプリケーションで活用されるようになると期待されるが、一方でAIが処理するべき計算の複雑さは指数関数的に増加し、超高速な演算処理が求められるようになってきた。

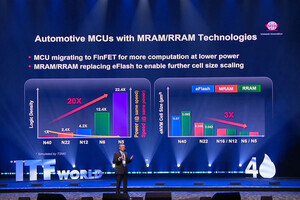

それに対応するためにロジックプロセス技術は継続的な進化を続けてきた。TSMCも20nmプロセス(N20)までは伝統的なプレーナ構造のトランジスタ形成を採用してきたが、16nmプロセス(N16)以降はFinFET構造を採用し、2025年から量産を開始する予定の2nmプロセス(N2)以降はナノシート構造のGAA(ナノシートGate All Around)が採用される。そして、将来的にはCFET構造の採用も検討されている。

こうしたデバイスアーキテクチャの進化にともない、リソグラフィもKrFからArFドライ、ArF液浸、そしてEUVへと進化。1つのパターン形成にかかる露光回数もシングルパターニングから複数回露光のマルチパターニングへと変化を遂げている。10nmプロセス(N10)までは、単純な寸法の縮小で所望の性能を実現できたが、7nmプロセス(N7)以降の1桁nmプロセス時代ではDTCO(デバイス設計・プロセス技術同時最適化)によるPPA(Power、Performance、Area:消費電力、性能、シリコン面積)のバランス最適化の必要性が生じたほか、最先端領域では「STCO(システム設計とデバイス製造設計、プロセス技術の同時最適化)」が必須となってきている。

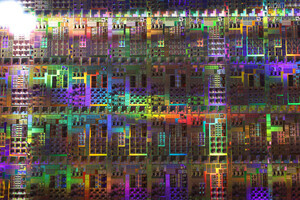

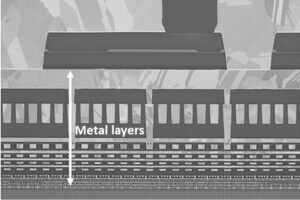

最先端のナノシートベースのロジックデバイスの断面写真を見るとわかるが、とても複雑である。ナノシートトランジスタの上部に形成されるBEOLプロセスと材料では、RC遅延の改善とロジック密度の向上が求められ、ナノシートトランジスタそのものには、構造的な革新やDTCOの採用による優れた電力効率の実現、そしてその下部には裏面コンタクトによるゲート密度とデバイス幅の柔軟性の確保が求められる。この裏面配線により、電源供給と性能向上が期待できるようになる。

GAAの後、将来的にはCFET構造の採用が検討されているが、CFETではこれまで平面に並べてたPMOSとNMOSを上下に配置することによりトランジスタ密度がナノシート比で1.5〜2倍に増えることとなる。

異種チップの集積でCoWoSは大型化しSystem-on-Waferに

優れたトランジスタ性能と、より高密度なパッケージングの実現には、2次元(平面)方向の進化であるプロセスの微細化の推進に加えて、3Dスタッキングと2.5Dの高度なパッケージング技術の同時導入が必要となる。また、将来のシステムスケーリングとパフォーマンスのニーズに対応するためには、3Dチップ間相互接続密度の向上が不可欠となっている。

過去数十年にわたって、パッケージ内のチップ間相互接続密度は向上を続けてきた。TSMCが提供するSoIC、InFO、CoWoS(Chip-on-Wafer-on-Substrate)などの高度なシリコンスタッキングおよびパッケージング技術は、チップ間の相互接続ピッチの縮小を継続してきたが、3D相互接続密度をさらに高める必要がある。

高度な集積を果たすことで、データ転送速度の向上、レイテンシの短縮、消費電力の最適化などがなされるようになり、コンピューティングシステム全体のパフォーマンスが向上するためである。性能を向上させつつも、消費電力を低減する、こうした需要が続くことで、システムレベルの異種チップ集積が急速な成長を見せるようになってきた。

例えばCoWoSテクノロジは、2023年の3.3レチクル(レチクル面積の3.3倍)からまもなく5.5レチクルに拡大し、今後数年で8レチクルを超えると予測されている。さらに、SoW(System-on-Wafer)テクノロジは、CoWoSを活用してコンピューティングパワーを新たな高みに引き上げると期待されている。SoWでは、高帯域幅メモリ(HBM)と垂直に積み重ねられたコンピューティングチップレットを統合することで、数年後の導入時にこれまでにないコンピューティングパフォーマンスの実現が期待されている。

このほか、光トランシーバ技術は将来のAIシステムにとって重要であり、チップ間の高速かつ低エネルギーで信頼性の高いデータ伝送を可能にする。TSMCのCompact Universal Photonic Engine(COUPE)テクノロジーは、SoIC-Xプロセスを使用することで、電気ダイとフォトニックダイをシームレスに積み重ね、消費電力とレイテンシの削減を可能とする。今後もシリコンフォトニクスの進化によって、PCB、基板、インターポーザレベルへと光エンジンの搭載が進むことで、レイテンシと電力の削減に対するメリットを得られるようになることが期待されている。

3D ICの実現に必要となる業界全体の協力体制

3D ICの設計において顧客は、SoCの設計と比べてより複雑な問題に直面することになる。将来の3D ICの構成例としては、SoICを中心に、3D集積メモリ、シリコンフォトニクス、RDLインターポーザ、組み込みコンポーネントなどが集積される見込みである。このためには、3D IC固有のEDA ツール、ダイ間インタフェースIPによる接続、HBM、基板、複数チップまたはチップレットの統合テストなど、多岐にわたる課題を解決する必要があり、こうした複雑さに対処するためにさまざまな分野のパートナーの協力が必須となる。

また、3D ICの設計を効率化するためには、さまざまな設計段階でEDAツール間のシームレスな相互作用も不可欠であり、この実現にはアーキテクチャとプロトタイピングから設計の実装とサインオフまで、設計プロセス全体をサポートできる業界標準の言語が必要となるとする。

なお、同氏は講演の終わりに「デバイス・プロセス技術、システムレベルのスケーリング、顧客固有の設計エコシステムの進歩を含む半導体のイノベーションは、AI時代の急速な技術進歩を推進する上で引き続き極めて重要である。TSMCは、次世代のテクノロジー、システム集積プラットフォーム、設計エコシステムに向けた一連の新しいイノベーションを積極的に推進している。これらの取り組みは、今後数十年間に高まるエネルギー効率の高いデータ集約型コンピューティングに対する社会的需要を満たす上で極めて重要になるだろう」と語り、今後も半導体のプロセス技術の進化、ならびにパッケージング技術の進化、そしてそれを実現するためのエコシステムの拡充が重要であると強調し、そうしたイノベーションの創出に向けてTSMCとしては全面的に支援を行っていくことを強調していた。