図研は11月26日、12月11日~13日にかけて東京ビッグサイトにて開催される半導体産業の国際展示会「SEMICON Japan 2024」に出展し、3D-ICやチップレット、先端半導体パッケージの設計や、半導体製造装置開発などを支援するソリューションを展示することを発表した。

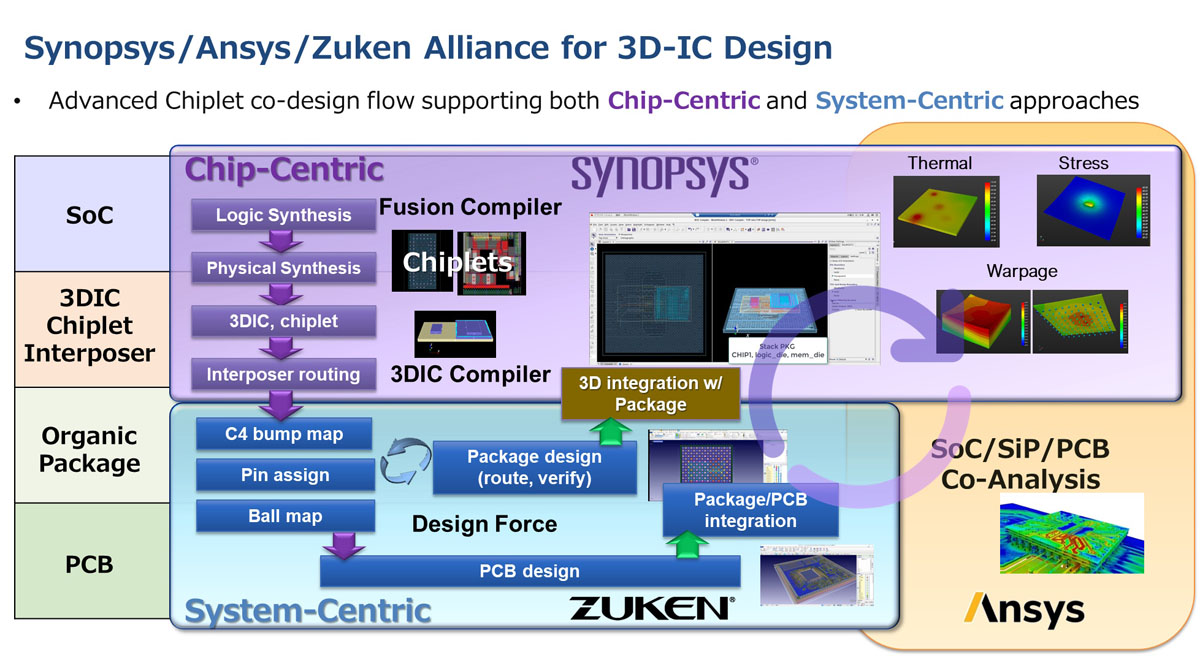

出展エリアはSEMICON Japan 2024より新設された次世代の半導体設計と検証分野にフォーカスする主要EDAベンダを集めた「ADIS(Advanced Design Innovation Summit)」で、テクノロジーパートナーであるSynopsysならびにAnsysのブースと協調する形で、これからの半導体開発を総合的に支援する設計ソリューションを紹介するという。

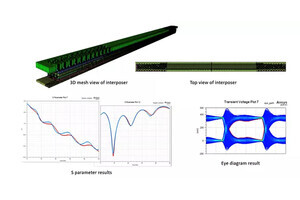

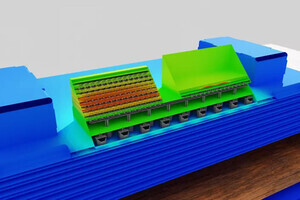

半導体の高性能化に向けてモノリシックな1つのダイにさまざまな機能を搭載するのではなく、個別の機能を最適なプロセスを使って製造したダイごとに分けて、それを1パッケージに集約する先端パッケージング技術に注目が集まっている。しかし、そうしたチップレットや3D-ICと呼ばれる技術は、ダイ/チップ単体での設計・解析のみならず、チップ間やインターポーザ、パッケージまで含めたシステムとしての設計・解析環境が求められることとなる。同社では今回、そうしたニーズに対応可能な新たな3D-IC設計・解析をターゲットにした総合的な開発環境の提供に向けてSynopsys、Ansysと協調した取り組みを紹介していくとするほか、3社合同セミナーなども行う予定としている。

なお、3社連携の取り組みとしては、チップレット設計で業界標準となりつつあるSynopsysの3DIC Compilerと、図研のシステムレベルマルチボード設計・検証環境「CR-8000 Design Force」をシームレスに連携した設計フローをサポートする機能を開発しているとするほか、すでにCR-8000 Design Forceとタイトに連携しているAnsysの解析ソリューションを加え、先端半導体パッケージ設計において必要とされるシステム全体を考慮した開発環境を実現しているともしている。