仏Yole Groupの半導体市場調査子会社Yole Intelligenceによると、先端パッケージングの中でも「ハイエンドパフォーマンスパッケージング」に位置づけられる2.5D/3Dパッケージング市場は、2023年は43億ドル規模だが、2029年まで年平均成長率(CAGR)37%で成長し、2029年には280億ドルを超すまでに成長すると予測されるという。

その適用市場を見ると、最大市場は「通信およびインフラストラクチャ」で、2023年は全体の67%を占めるという。また、出荷数量については2023年の6億2700万個からCAGR44%で成長し、2029年には56億個に到達すると予測されている。

HBMや3D NANDに代表される3D積層メモリは、2029年までに市場の70%以上を占めるまでに成長することが予測され、同社では急成長しているプラットフォームとして、CBA DRAM、3D SoC、アクティブSiインターポーザ、3D NANDスタック、および組み込みSiブリッジを挙げている。

こうした2.5D/3Dパッケージングは現在、ファウンドリ、OSAT、IDMが混じって競争する状態となるなどサプライチェーンの境界があいまいになっており、小規模なプレーヤーが競争を有意に進めることが難しくなっている。また、技術的な難易度も上昇し続けており、そのサプライチェーンへの参入障壁が高まりを見せている。

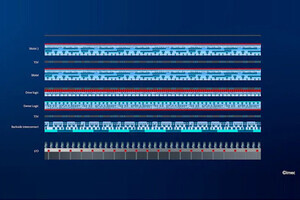

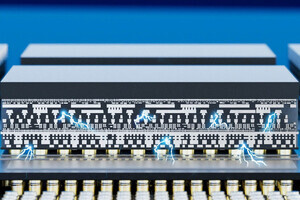

TSMCは、CoWoS、InFO、3D SoICソリューションを活用した「3DFablic」を展開するなど、前工程も後工程を付けた付加価値ビジネスで成長を続けており、TeslaとCerebrasにInF_SoWソリューションを提供しているほか、3DSoIC、CoWoS、InFOソリューションなどをAMD/Xilinx、GUCなどに活用してもらっており、業界のリーダーであり続けることを確実にしている。このほか、IntelやSamsungも独自技術を展開して存在感を示しているほか、ソニーが2015年以降、ウェハ・ツー・ウェハ技術を用いたハイブリッドボンディングチップを最も多く出荷している企業といえるとする。同社は現在、2スタック版と3スタック版を出荷しており、中でも3スタック版は、2スタック版が画素が回路の上という構成に対し、画素が回路の上にあるDRAMバッファキャッシュの上に積み重ねられる構成になっているという。

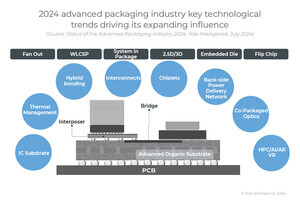

ムーアの法則の限界を破るパッケージング技術

ムーアの法則の実現をけん引してきたプロセスの微細化は技術の複雑化とコストの上昇を招いており、その打開策として、2.5D/3D化によるシステムレベルのスケーリングが採用されるようになった。特にチップレットの活用により、SoCのチップを各機能ごとに分離することを可能とし、演算能力を高める部分だけを先端プロセスで製造するといったコスト最適化を図ることができるようになった。

なお将来に向けては、I/Oピッチの微細化や、2.5Dと3Dの統合などさまざまな機能の統合が期待されているという。