imecは、オランダの「ASML-imec high-NA EUV Lithography Lab」にてNA=0.55の高NA EUV露光装置を用いてロジックデバイスおよびDRAMパターンを露光した結果を公表した。

それによると9.5nm(19nmピッチ)のランダムロジック構造、中心間距離30nmのランダムビア、22nmピッチの2Dパターン、および32nmのDRAMパターンが、imecの高度パターン形成プログラムの枠組みの中で高NA EUV向けに最適化された材料とベースラインプロセスを使用して、1回の露光で形成されたという。これらの結果を踏まえimecでは、1回の露光で高解像度の高NA EUVリソグラフィを可能にするエコシステムの準備が整ったとしているほか、従来のEUVでは複数のマスクレイヤを必要としていた微細な回路を1回の露光で置き換えることができる高NA EUVの優位性を示すものだともしている。

これらの結果についてimecとASMLは、パートナーと緊密に協力して、第1世代の高NA EUVリソグラフィのパターン形成エコシステムと計測に向けた集中的な事前作業の結果として得られたものであると説明。露光に先立ち、imecは専用のレジスト、下層、フォトマスクなどを準備し、高NA EUVベースラインプロセスとして光近接効果補正(OPC)、統合パターン形成およびエッチング技術など をNA=0.55の高NA EUV露光装置に移行したとしている。

imecのコンピューティング技術およびシステム/コンピューティングシステムスケーリング担当シニアバイスプレジデントであるSteven Scheer氏は「初期検証として、ASMLとimecの共同ラボで世界初の高NA対応ロジックおよびメモリのパターニングを実証できた。この結果は、高NA EUVがスケーリングされた2次元構造のシングルプリントイメージングを可能にし、設計の柔軟性を向上させるとともに、パターニングのコストと複雑さを軽減するという独自の可能性を示している。今後はパターニング・エコシステムのパートナーに貴重な洞察を提供し、高NA EUV固有の材料とEUV露光装置がさらに成熟するようにサポートしていきたい」と述べている。

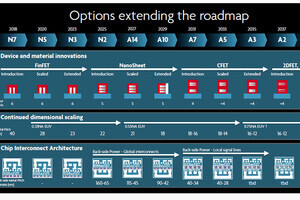

またimecの社長兼CEOであるLuc Van den hove氏は、「この結果は、1回の露光で20nm未満のピッチの金属層をターゲットとする、高NA EUVリソグラフィの予測されていた解像度能力を裏付けるものである。したがって、高NA EUVは、ロードマップを『オングストローム時代』にまで押し進める重要な柱の1つであるロジックおよびメモリ技術のスケーリングを継続する上で役立つ。これらの初期デモンストレーションは、ASMLとimecの共同ラボの設立によってのみ可能となり、imecの研究パートナーが先端半導体製造への高NA EUV露光装置の導入を加速するに役立つだろう」と述べている。

なお、imec-ASML High NA Labにてimecの顧客などはASMLの高NA EUV露光装置「TWINSCAN EXE:5000」にアクセスすることが可能で、独自の設計ルールとレイアウトを活用してプライベートな高NA EUVユースケースを開発できるようになっているという。