Lam Researchは、次世代ロジックや3D NAND、高度なパッケージングアプリケーションにおける主要な製造課題に対処するために、シリコンウェハ・ベベル成膜を実現する装置「Coronus DX」を開発したことを発表した。

半導体のプロセス微細化に伴い製造ラインでは数百のプロセスステップを処理する必要が生じるようになっている。同製品は、ワンステップでウェハエッジの両面に独自の保護膜層を堆積し、半導体製造中に発生する欠陥や損傷を防止することを可能とするもの。ベベル部の保護が可能になることで製造歩留まりが向上し、チップメーカーは次世代チップ製造のための新しい最先端プロセスを実装できるようになるという。

Lam Researchでは、2007年にエッジに沿って堆積層を除去することで欠陥を防ぐことができるベベルエッチング装置「Coronusファミリ」を市場投入しており、これまでに世界中で数千チャンバーが利用されてきたが、Coronus DXは、同ファミリに追加されたエッジに酸化膜を堆積するための装置という位置づけとなる。

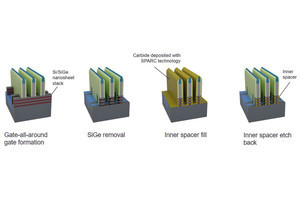

具体的には、積層を繰り返すとウェハのエッジに沿って残留物や粗さが蓄積し、それらが剥がれ落ち、ほかの領域に移動することで、半導体デバイスの故障の原因となる欠陥が生じる可能性がある。例えば、3Dパッケージにおいては、BEOLからの材料が残渣として残り、その後の処理で汚染源となる可能性がある。また、3D NAND製造における長時間のウェットエッチングプロセスに伴い、エッジが基板に対して損傷を与える可能性があり、これらの欠陥をエッチングで除去できない場合、同装置がベベル上に薄い誘電体保護層を堆積。これにより、半導体の品質に影響を与える可能性のあるこれらの問題の解決を図ることができるようになると同社では説明している。

LetiがLam Researchに技術的支援

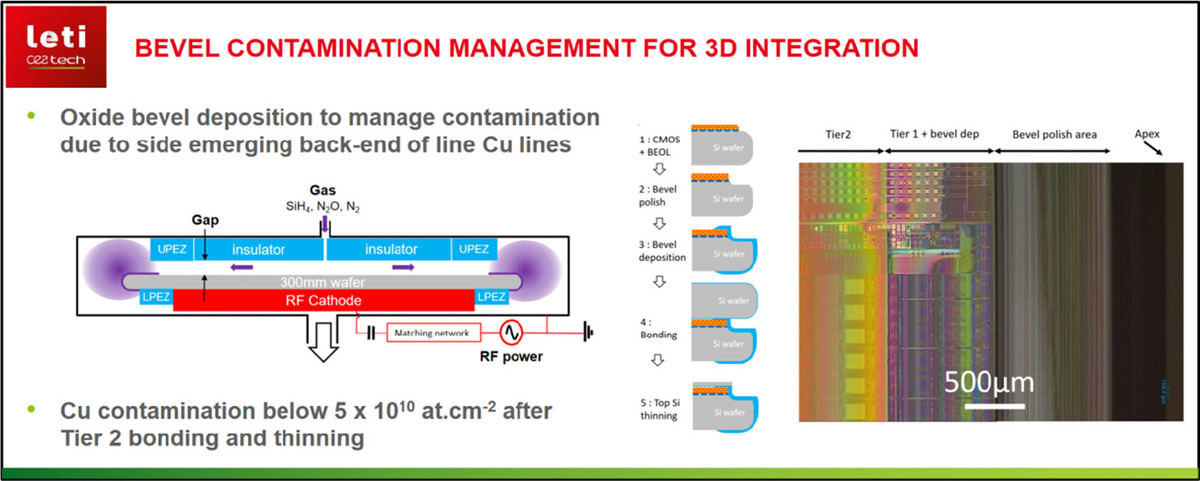

なお、フランスの国立研究機関CEA-Letiの半導体プラットフォーム部門責任者のAnne Roule氏は、「CEA-Letiはその専門知識を応用し、Lam Researchが先進的な半導体製造における重要な課題に取り組むのを支援した。3D実装を簡素化することで、歩留まりが向上し、チップメーカーが画期的な生産プロセスを採用できるようになる」とコメントを寄せている。なお、ベベル成膜技術技術の詳細については、CEA-LetiとLam Researchの共著論文「Bevel contamination management in 3D integration by localized SiO2 deposition」に詳述されている。

-

3次元積層のためのベベル汚染制御の概要 (出所:「Bevel contamination management in 3D integration by localized SiO2 deposition」)

また、Coronus DXのユーザー企業の1社であるキオクシアでメモリプロセスの技術責任者である宮島秀史氏もコメントを寄せており、「ベベル技術などの分野の進歩を通じて生産プロセスの品質を向上させることは、次世代のフラッシュメモリを顧客に提供するために不可欠である。キオクシアは、Lam ResearchおよびCoronusソリューションと引き続き協力して、最先端のウェハ生産を可能にすることを楽しみにしている」としている。