TSMCが2nmプロセスでの試験生産に向けた準備を開始した模様だと複数の台湾メディアが報じている。

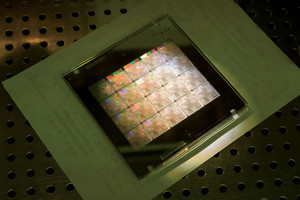

それによると台湾北部のTSMC本社近くの新竹科学園区の研究開発センターに1000人以上のエンジニアを招集、量産に向けたチームを結成し、2023年末までに1000枚近い300mmウェハによる試験生産を開始することを目標としており、その後、2024年のリスク生産、2025年の量産を予定している。

TSMCからは、噂についてはコメントしないとしたうえで、「2nmプロセスの研究開発は順調に進んでおり、量産は計画通り2025年に予定されている」としている。

2nmファブは新竹と台中に合計6棟計画

TSMCでは、新竹市の宝山用地(新竹県宝山郷)第2期区画に2nmプロセス採用のギガファブ「Fab20」4棟を設置する計画である。その後、BCP含めたリスク分散のために、台中の中部科学園区にさらにファブを2棟建設する計画で、合計6棟の2nmファブが建設される計画である。国家科学・技術委員会(NSTC)によると、中部科学園区の2nmファブ建設用地は、2023年11月に用地取得などの手続きが完了し、同年12月より利用可能になる見通しだという。

GAA構造の採用のほか、裏面電力供給も計画

TSMCによると、2025年に「2nmプロセス(N2)」の量産が開始された後、2026年には裏面電力供給方式のバックサイド・パワーデリバリ(BSPD)を採用した「N2P」、ならびにHPC向けにパフォーマンスを向上させた「N2X」をそれぞれリリースする予定だという。

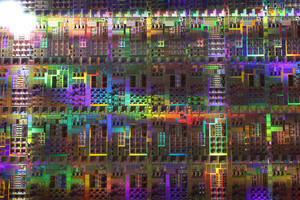

2nmトランジスタは、3nmまでのFinFET構造ではなく、TSMC初となるナノシートトランジスタ構造のゲート・オール・アラウンド(GAA)技術が採用される。同社では、これまでにトランジスタ構造の進化に伴い、2nmプロセスは3nmプロセスに比べて高性能化することから、顧客の採用意欲も3nmプロセスがリリースされた当初よりも高くなるとの見方を示しており、最初の顧客としてAppleやNVIDIAの名前が取りざたされている。

また、2nmプロセスではトランジスタ構造の変化に加えて、製造技術面でも大きな変更が加えられるという。もっとも大きな変更点は、EUV露光のための計算リソグラフィ(Computational Lithography)プロセスが、従来のCPU方式からNVIDIAのDGX H100をベースとした新しいAIシステムに変更される点で、これによりコンピューティング効率が向上し、サーバの消費電力も削減されることになるほか、フォトマスクの生産性も向上するという。台湾サプライチェーン関係者の話では、TSMCとNVIDIA、ASML、米Synopsisの4社の協業で実現したという。

NVIDIAのジェンスン・フアンCEOは先般開催されたCOMPUTEX 2023に参加するために台湾を訪問した際、TSMCがNVIDIAなどのパートナーと取り組んできたAIシステムを、2nmプロセス用計算コンピューティングシステムに6月より適用する予定だと語っていた模様で、これにより従来比で演算時間が40分の1に短縮できると述べていたという。このほか、2nmプロセスでは、従来とは異なるさまざまな革新的手法が取り入れられる模様だが、詳細はまだ明らかにされていない。