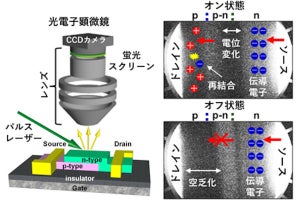

具体的には、自己凝集能力が高い傾向にある高性能n型ポリマー半導体材料に対し、UFTMの最適化を実施するのと同時に、電極から電子を注入するときの障壁を下げ、理想的なnチャネル型FET特性を得る方法も開発することで、実用的な性能を持つnチャネル型FETの動作実証に成功したとする。

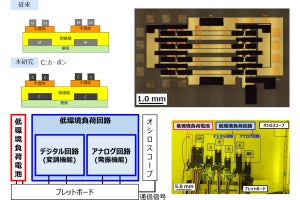

今回の研究成果により、超フレキシブルCMOS回路を実現するための第一段階の要素技術がそろったことから、研究チームでは次のステップとして、今回開発されたnチャネル型FET作製法と、すでに開発されているpチャネル型FET作製法を組み合わせ、CMOS論理回路の最小構成要素であるCMOSインバータ回路の作製を目指すとしており、併せてシリコンCMOS回路の模倣ではなく、ポリマー半導体とUFTM法ならではの優れた点を活かした新しいデバイス構造と配線接続方法などを開発していくとしている。

また現在、皮膚などの凹凸があり伸縮性がある表面に転写することができる電子タトゥーという電子回路が揺籃期にあることを踏まえ、研究チームでは今回の研究を発展させることで、これまで硬くて厚みのあるシリコンLSIに頼らざるを得なかった高度な演算機能や通信機能を内蔵することができ、より実用的な電子タトゥーが実現されることが期待されるともしている。