千葉工業大学(千葉工大)は11月24日、脳の数理モデルであるスパイキングニューラルネットワーク(SNN)を用いることで、深層学習の超低消費電力ハードウェアであるアナログ演算回路「In-memory computing(IMC)回路」を高性能化する仕組み「RC-Spike」を考案し、数値シミュレーションでその効果を実証することに成功したと発表した。

同成果は、千葉工大数理工学研究センターの酒見悠介上席研究員、九州大学大学院 総合理工学研究院の森野佳生准教授、九州工業大学大学院 生命体工学研究科の森江隆特任教授・名誉教授、NEC デジタルテクノロジー 開発研究所の細見岳生主幹研究員、東京大学の合原一幸特別教授・名誉教授(東大 国際高等研究所 ニューロインテリジェンス国際研究機構副機構長/千葉工大 数理工学研究センター主席研究員(嘱託)兼任)らの共同研究チームによるもの。詳細は、IEEE主催の回路とシステムに関する国際学会「ISCAS 2022」にて発表された。

実社会で深層学習を運用するにあたっては、認識性能などのアルゴリズム的な性能だけでなく、物理的制約を考慮する必要があり、中でも消費電力は重要な要素の1つとされている。深層学習は一般的に消費電力が大きいため、バッテリー容量が限られる小型デバイス上での駆動が困難とされることから、消費電力の低減が現在のAI研究の重要課題の1つとなっている。

消費電力を低減する最も直接的な方法の1つに、専用ハードウェアを作製するというものがある。数あるハードウェア方式の中で、特に電力効率に優れるのがIMC回路で、その原理は単純で、抵抗に流れる電流を足し合わすことで、深層学習のコアの演算である積和演算を行うというものとなっている。

IMC回路はこれまで、「既存のアルゴリズムをハードウェアにマッピングする」という、一般的なトップダウン的発想のもと開発が進められてきたという。そこで研究チームは今回、IMC回路のさらなる高性能化を目指し、脳のモデルであるSNNを応用することにしたとする。

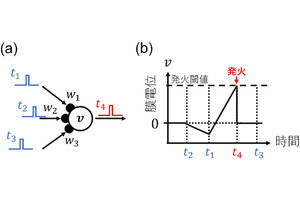

SNNを回路化し、知能システムを構築する研究「ニューロモルフィックエンジニアリング」は、“回路をニューロンと見なし、それらをつないでネットワークを構築した上で学習させる”というボトムアップ的な発想に基づいたものであり、今回の研究では、このボトムアップ的な発想をもとに、IMC回路の再構成が目指された。