低消費電力プラットフォームを拡張するAI/IoT向け「N6e」

TSMCでは、2020年のTechnology Symposiumで発表したN12eテクノロジの成功を受け、次世代プロセス「N6e」の開発を進めているという。これはエッジAIおよびIoTデバイスに必要なコンピューティングパワーとエネルギー効率を提供するように調整されたプロセステクノロジーの進化形で、TSMCの7nmプロセスに基づいており、N12eの3倍のロジック密度が期待とする。

これは、TSMCの超低消費電力プラットフォーム、ロジック、RF、アナログ、組み込み不揮発性メモリ、およびエッジAIとIoTのアプリケーションを対象とした電力管理ICソリューションの包括的なポートフォリオの一部として機能するとしている。

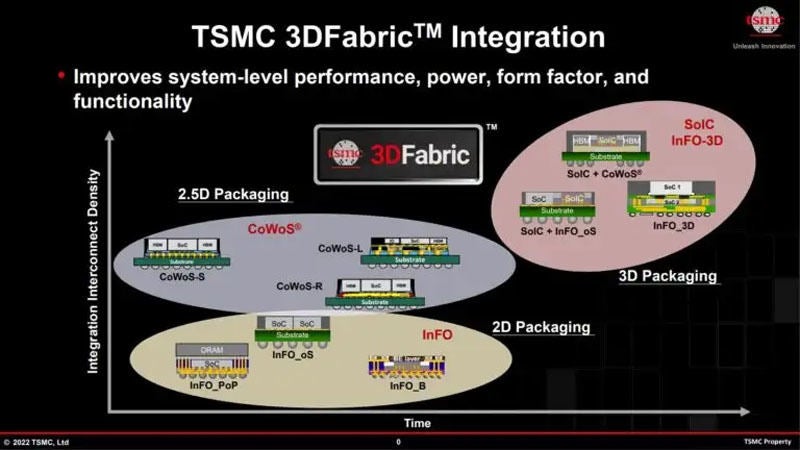

TSMC 3DFabric(3次元シリコンチップ集積)

またTSMCでは、TSMC-SoICチップスタッキングソリューションとして以下の2つのアプリケーションも紹介している。

- チップオンウェハ(CoW)テクノロジーを採用してSRAMをレベル3キャッシュとしてスタックするSoICベースのCPU

- Wafer-on-Wafer(WoW)テクノロジーを使用して、ディープトレンチコンデンサダイの上に積み重ねられたインテリジェンスプロセッサ

N7(7nmプロセス)採用のチップはすでにCoWとWoWの両方で生産されており、N5(5nmプロセス)のサポートも2023年に予定されている。また、SoICおよびその他のTSMC 3DFabricシステム統合サービスに対する顧客の需要を満たすために、完全自動化3DFabric工場を2022年後半にも台湾北部の竹南で稼働させる予定としている。

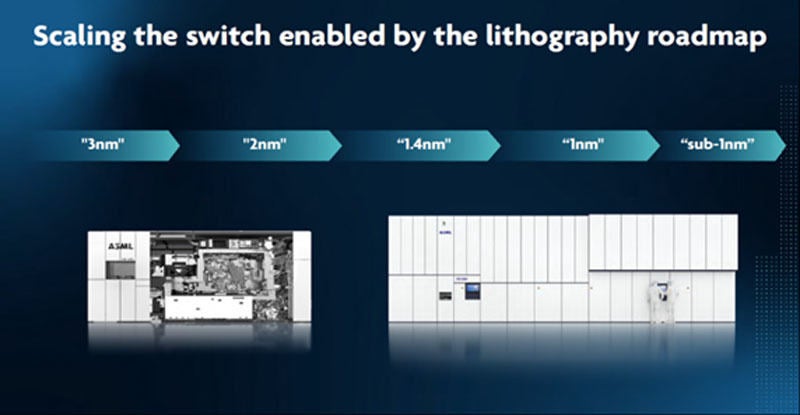

2024年には高NA EUVリソグラフィの導入を計画

なお、同社研究開発担当上級バイスプレジデントのY.J.Mii氏が、次世代EUV露光装置である高NA(NA=0.55)EUV露光装置をASMLから2024年にも調達することを明らかにした。

ただし、導入してすぐに2nmプロセスの生産に使うことは考えておらず、当初は、さらに先の微細化プロセス研究開発用に適用し、十分に使い慣れてから生産に導入するとしている。

-

EUVリソグラフィのロードマップ。左が現在の量産に適用しているNA=0.33のEUV露光装置、右が開発中のNA=0.55の高NA EUV露光装置 (出所:imec Technology Forum Belgium 2022,2022年5月)

同社のTechnology Symposiumはコロナ禍にあった過去2年は、オンラインで開催されてきたが、2022年は対面式のイベントとして開催されており、米国に続き、欧州や中国、台湾などでも同様にリアルなシンポジウムとして開催される予定となっている。