2021年12月に開催された「SEMICON Japan 2021 Hybrid」において、同年、茨城県つくば市に2021年に開設された「TSMCジャパン3DIC研究開発センター」を含め、TSMC全体の後工程技術開発を指揮する同社Specialty & Packaging Manufacturing Management担当DirectorのChris Chern氏が「3D Fabric Development Focuses including Advanced Packaging and Intelligent Manufacturing(先進パッケージングとインテリジェント製造を含むTSMC独自の3DIC実装の焦点)」と題し、同社の後工程実装技術と日本の研究開発拠点での活動について台湾からオンライン講演した。

また、2022年1月に開催された「第37回インターネプコン ジャパン(インターネプコン2022)」では、TSMCジャパン3DIC研究開発センターのセンター長に就任した江本裕氏が、同センターの取り組みについて講演した。

江本氏は、 ルネサス エレクトロニクスにて資材調達、営業マーケティング、経営企画などを担当したのち、ジェイデバイス(東芝、富士通、ルネサスなどの後工程工場を譲り受けたOSAT)の代表取締役社長に就任。2021年、TSMCに転じて3DIC研究開発センター長に就任した。

2.5D/3D化が進むこれからの半導体

ICの高集積化を今後も進めていくためには、回路パターンを微細化し、密度を高める従来の手法が物理的な限界が近づいているため、異種プロセスで製造した複数の半導体チップを混載し、縦方向(3次元)に集積する手法に注目が集まっている。

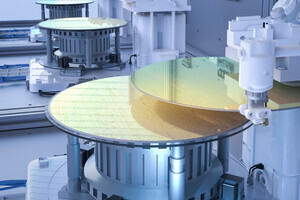

Chern氏は、「この10年ほどの間に、シリコン・インタポーザを用いて、その上に複数チップを実装する2.5D技術が活用されるようになった。そして最近では、配線遅延の短縮を狙って、多くのメーカーが3D技術へと移行しつつある」とする一方、「後工程の高密度化には、前工程にはない2つの技術的難しさがある。1つは、製造するチップの仕様や応用に応じて、多様な後工程技術を使い分けながら製造する必要がある点。もう1つは、前工程によって生じたチップの個体差を勘案しながらチップやインタポーザを積層して、高度なチップに仕上げる必要がある点である」と技術的な難しさを説明した。

同氏は、TSMCでの実装技術の変遷について、「10年ほど前から、「InFO(Integrated Fan-Out)」と「CoWoS(Chip-on-Wafer-on-Substrate)」と呼ぶ、2.5D実装技術を投入してきた。最近は、3D技術であるSoIC(System on Integrated Chips)も量産に適用するようになった」と現状を説明したほか、「TSMCは、2.5Dと3Dの組み合わせにより『3DFabric』という独自の技術体系を確立した。3DFabricは、機能の異なる集積回路をつなぎ合わせるヘテロジニアスインテグレーション技術であり、線幅(技術ノード)の異なるチップを1つのチップのようにつなぎ合わせる事が出来る。集積化のフレキシビリティに加えて、低レイテンシ、高速性、信号伝送帯域幅の広さ、さらには集積回路における高いバンプ/バンプレスコンタクト密度がすべて実現できる」と、自社の技術の優位性を強調した。

同氏は、実装工場の責任者として、3DFabric技術の無欠陥製造が可能な量産工場を確立するためには、スマートな最先端工場にしなければならないとする。その実現のためには、以下の3点と、自動欠陥検出および自動欠陥分類(ADC)警告機能によるプロセス精密制御の組み合わせる必要があるとしている。

- 完全なデータメーションシステムと全レベルでの完全な仕掛ウェハトレーサビリティに基づく製造装置と自動化仕掛ウェハのハンドリング、

- プロセスと計測装置、および仕掛ウェハ自動ハンドリングシステムの相互通信を実現するAIoT(人工知能+IoT)とマシンラーニング

- 計測とセンサの統合によるすべての生産ステップのきめ細かな計測、モニタリング、監視

このような複雑な生産管理を実現するには、人手ではなくIoTによるダイレベルの解析とプロセス条件の個別最適化が必要になってくる。Chern氏は「我々は、ラインで収集したデータを基にシミュレーションを実施し、ラインに不具合が発生する前に兆しを察知し、先回りして対処できる体制の確立を目指している」と述べ、ここに3DIC研究開発センターを日本に開設する意義があると述べた。先端技術の開発、運用については「サプライヤとの相乗効果が必要」であり、そうしたパートナーが多い日本で取り組みを進めることで、スマート工場の実現を果たそうとしている。

日本で研究開発を進める意味

一方の江本氏も、将来のコンピューティング需要を満たすには、半導体デバイスのさらなる集積化・高性能化を実現する3Dパッケージ技術の開発が不可欠であるとしている。

その実現のためにTSMCは、つくば市の産業総合研究所(産総研)内のスーパークリーンルームにR&Dラインを設置し、多数の素材・製造装置メーカー、産総研、大学などと連携することで、最先端技術を開発することを目指すとしている。すでに開発パートナー企業としては20社以上の名前が挙がっているが、そうしたパートナー企業の多くが、すでにTSMCやimecにも人材を派遣して、同種の研究協業を進めていることから、後発となるつくばセンターがそうした先行している研究とどのようにすみ分けるのかははっきりしていない。

なお、経済産業省(経産省)は、先端半導体製造技術の開発事業において、TSMCジャパン研究開発センターを実施者に選び、今後5年間の研究費380億円の半額である190億円を助成することにしている。TSMCのC.C.Wei社長は、「日本では、熊本にスペシャルティテクノロジーの前工程ファブを建設することにしているが、後工程工場を建設する計画はない」と述べており、日本での研究開発成果についても台湾で活用するとみられる。