東北大学は6月1日、3つの新技術を取り入れた新設計の「4重界面磁気トンネル接合素子」(Quad-MTJ)を開発し、18nmの接合直径において、保持特性と高速での書き換え耐性を実証することに成功したと発表した。

同成果は、東北大 国際集積エレクトロニクス研究開発センターの遠藤哲郎教授(同センター長兼任)らの研究チームによるもの。詳細は、6月13日から19日までオンライン開催される国際会議「2021 Symposia on VLSI Technology and Circuits」で発表される予定だ。

IoT時代の本格化に伴い、生み出されるデータの量は爆発的に増加することが見込まれており、その処理のために多くのプロセッサやメモリが用いられると見られている。しかし、単に数を増やせばよいわけではなく、環境負荷の低減などの観点から、それらの半導体の低消費電力化が求められることとなっている。メモリとしては、不揮発性メモリの活用が期待されているほか、ロジック半導体についても不揮発化の研究開発が各所で進められている。こうした不揮発性ロジックやメモリで情報の記憶を担う役割を担うことが期待されている技術の1つがスピントロニクスである。

現在、22/28nmプロセスを用いたSTT-MRAMを搭載したロジック半導体が製品化され、14/16nmプロセスの適用が期待されるようになっている。一方、最先端の半導体プロセスは現状5nmに到達しており、4nmや3nmプロセスの実用化も目前とされており、STT-MRAMプロセスとのギャップが生じており、そうした1桁nm世代におけるSTT-MRAMのスケーリングの実証が求められているという。

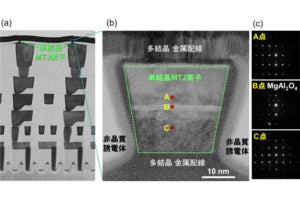

こうした背景のもと、東北大では長くSST-MRAMの根幹となる、磁気トンネル接合(MTJ)素子の研究開発が続けられてきており、2010年には、現・東北大総長の大野英男教授らの研究チームが、界面垂直磁気異方性(i-PMA)型MTJ素子を開発。その後、2014年に大野教授と遠藤教授による研究チームによって、i-PMAを2つ有する「Double-MTJ素子」が開発され、さらに2019年にi-PMAを4つにしたQuad-MTJ素子が開発された。

しかし、最先端の1桁nm世代の集積回路とMRAMを融合するためには、配線層に形成するMTJ素子の接合直径を1桁nmまで微小化する必要があるが、微小化に伴い、データ保持特性および高速書込み耐久性/回数が減少するといった課題が生じていたという。

そこで遠藤教授らは今回、新たな設計を行ったQuad-MTJ素子を開発、STT-MRAMとして両立が困難なデータ保持特性と書き換え耐性能のジレンマを解決することに成功したという。

-

今回の研究で開発された新設計のQuad-MTJ素子の構造面における3つの革新的技術。4重界面に加えて、(1)新低ダメージ技術により低い接合抵抗のMgO障壁層、(2)磁石(記録層1と記録層2)に磁気摩擦定数の小さい新材料、(3)1桁nm世代以降での磁気的安定性を補償する新参照層が用いられた。この3つの技術により、低消費電力化および高速の書き換え耐久性の向上が実現された (出所:東北大プレスリリースPDF)

しかも、18nmの接合直径において、以下の4点を同時に実証し、1桁nmの半導体ロジックプロセスのデザインルールに適合させることに成功したとしている。

- 10年間のデータ保持特性

- 1011回(1000億回)以上の書込み耐性

- 10ナノ秒の高速書込み動作

- 約2割の低消費電力化

なお、研究チームによれば、今回の成果により、アプリケーションプロセッサの設計コンセプトが一変され、その結果、MRAM技術を融合したアプリケーションプロセッサの応用領域が、画像処理やAIシステムなどのハイエンド応用から、IoTやセンサネットワークシステムなどのローエンド応用に至る領域において、低消費電力化と高性能化が進んでいくことが期待されるとしている。