Lattice Semiconductorは12月10日(米国時間)、かねてより開発を進めていた28nm FD-SOIプロセス製品の第1弾となる「CrossLink-NX」を発表した。また、今後は各プロセスを1つのプラットフォームとして、そのプロセス技術に基づいて、さまざまな製品を展開していくプラットフォームビジネスに移行すること、28nm FD-SOIが「Nexus」というプラットフォーム名で、その最初となることも発表された。

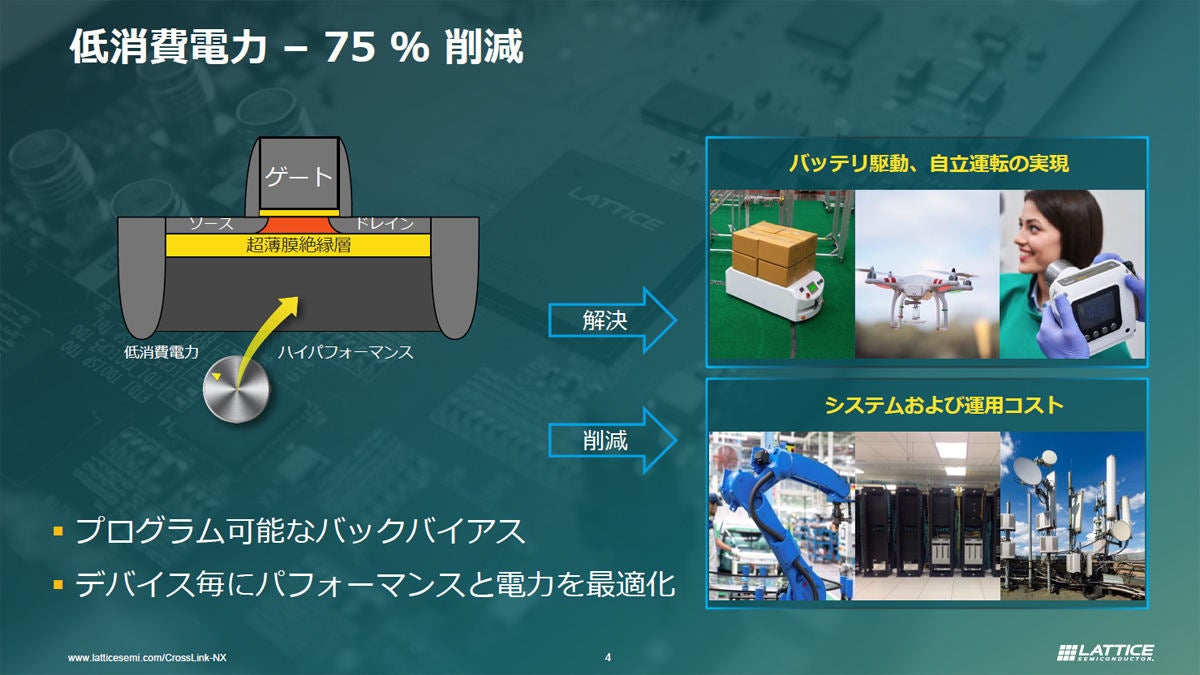

NexusプラットフォームのベースとなるのがSamsung Electronicsの提供する28nm FD-SOIプロセス。CrossLink-NX(NXはNext Generationの意味とのこと)では、これのバックバイアスの電圧を選択的に変更することで、適用するアプリケーションニーズに応じて、パフォーマンス性能を高くしたり、電力効率や低消費電力化を図ったりすることを可能とした。具体的には、競合製品(28nmプロセス品)比で75%の消費電力削減を可能にしたとする。

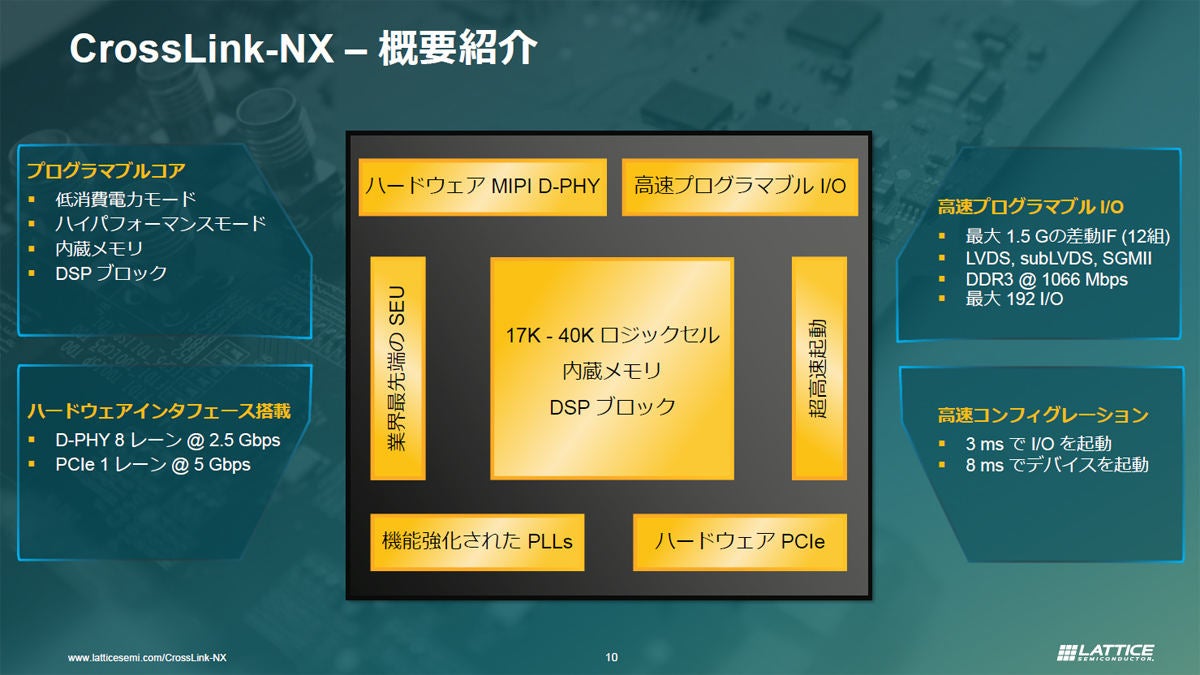

ハイパフォーマンス性といった面では、ロジックセルあたりの内蔵メモリを170ビットとすることで、AI処理の効率化を図ったほか、3msでのI/O起動、8msでのデバイス起動を可能とした。従来は、電源が入るとFPGAが立ち上がって、回路を読み込んでコンフィグを実施する必要があったが、回路などの工夫により、I/O部を先に高速立ち上げすることで、システム全体の使い勝手の向上を図ったという。

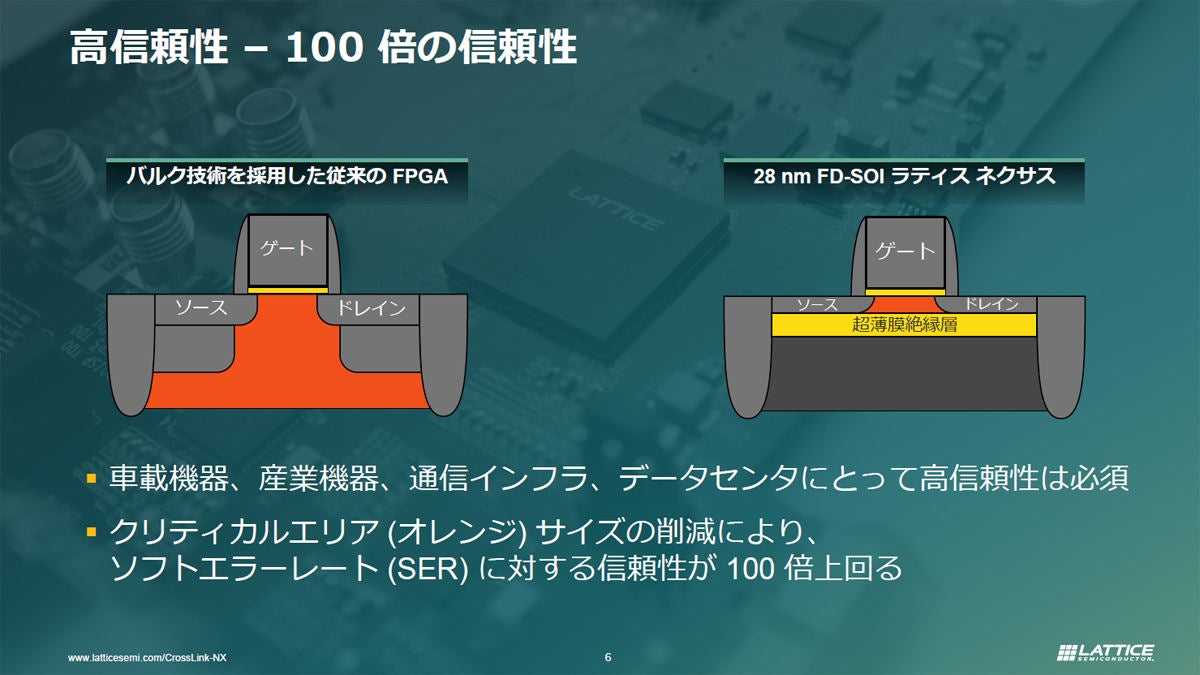

また、FD-SOIとしたことで、ソフトエラーを引き起こすボディ部の面積が縮小。これにより、ソフトエラーレートに対する信頼性がバルクシリコンを用いた競合のFPGA比で1/100に低減することができるようになったとする。

さらに、LUTを4ビット入力1ビット出力(LUT4。他社はLUT6)とすることで、配線領域の削減などを図ることができ、結果、チップサイズの小型化を可能としたとする(40Kのロジックセル数で6mm×6mm)。

このほか、プログラマブルI/Oも最大192、2.5GbpsのMIPI D-PHYといった機能拡充も図られており、「主にビデオインタフェース変換や画像処理、4Kサポートや複数のディスプレイのサポートなどといったニーズに対応できるようになった」と、Lattice Semiconductorのアジアパシフィック地域 事業開発担当ディレクターのYing Jen Chen(陳英仁、インジェン・チェン)氏は製品に対する自信を語る。

CroeeLinkはロジックセルが17Kの「CrossLink-NX-17」と40Kの「CrossLink-NX-40」の2製品がラインナップ。基本的には40K品のほうがDSPの数やPLLの数などが多いが、RAMブロックについては40K品が1Mビット、17K品が2.5Mビットと逆転している。これについて同氏は、「17K品で外部活用するのはサイズ的に難しく、内蔵メモリで処理をしないといけない、という判断から多めにした」と、その背景を説明する。

また、開発ツールは「Radiant」の最新版となる2.0が製品リリースと同じタイミングでリリースされており、ユーザーはそちらを使って開発を進めることとなる。

ちなみに、NexusプラットフォームとしてFPGAではなく、CrossLinkを第1弾製品として市場投入したことについて同氏は、「CrossLinkの既存ユーザーから、電力に対する要求とパフォーマンスに対するニーズが強く、かつロジックセルの増加も求められていた。背景にはエンベデッドビジョンのアプリは、ハードマクロで対応した方が使いやすいということもあり、FPGAよりも先に発表となった」と背景を説明。そのため、従来品のCrossLink Plusの後継品という位置づけではなく、「使えるIPも増えてきたし、かなりいろいろなことをできるようにしたデバイスという位置づけ」としている。

なお、CrossLink-NXのサンプル出荷ならびに評価ボードの提供はすでに開始済みだが、量産出荷については2020年末ころを17K品、40K品ともに予定しているという。