米Lattice Semiconductorは5月20日にRoT(Root-of-Trust)を搭載したMachXO3Dと、同社が従来から提供しているAI向けフレームワークであるSensAIのVersion 2.0をそれぞれ発表した。これに関する記者説明会が5月23日に日本法人であるラティスセミコンダクターで開催された(Photo01)。

実は同社、今年4月に発表された2019年第1四半期決算の資料の中で、次世代製品のテープアウトが完了したことをアナウンスしている。この次世代製品というのはSamsungの28FDSを利用した製品になる事は以前から説明されていたが、残念ながらこちらの製品に関しての説明は今回は無し。これについては「今年末には発表する」との話であった。

MachXO3にハードウェアRoTを内蔵

さて、まずはMachXO3D。ベースとなるのは同社が2014年から提供を開始しているMachXO3である。

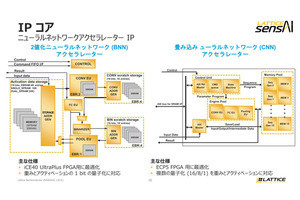

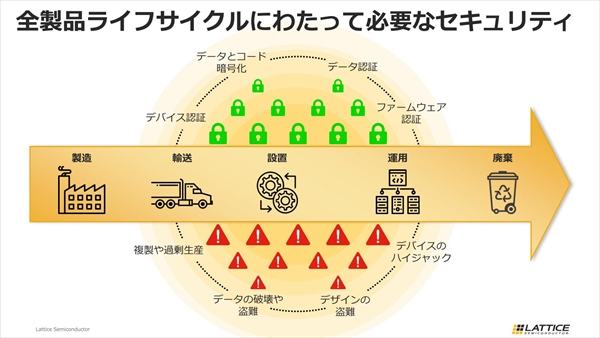

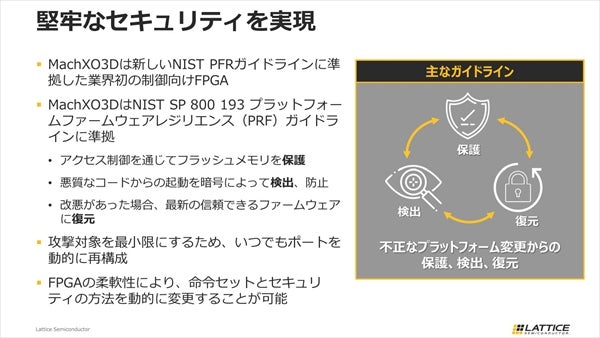

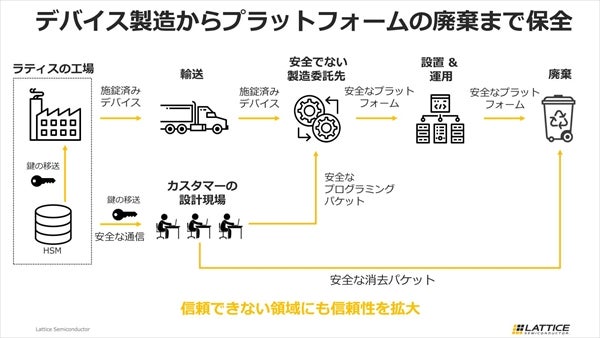

MachXO3は同社の中ではミッドレンジの製品で、Bridgeなどに広く利用されているが、昨今のセキュリティへの関心の高さに対応して、ハードウェアRoTを内蔵させた製品が今回のMachXO3Dとなる。これは、製品の全ライフサイクルに渡ってセキュリティ性を提供する(Photo02)もので、高いセキュリティ性と柔軟性の両方を提供できるとする(Photo03)。

-

Photo02:製品製造から製品破棄までのすべての過程で、必要なセキュリティ(製造なら不正コードの侵入を防ぐことだし、破棄なら製品内のデータを読み取れない様にすることがこれにあたる)

-

Photo03:NIST SP(Special Publication) 800-193は昨年5月に発表されたばかりのもの

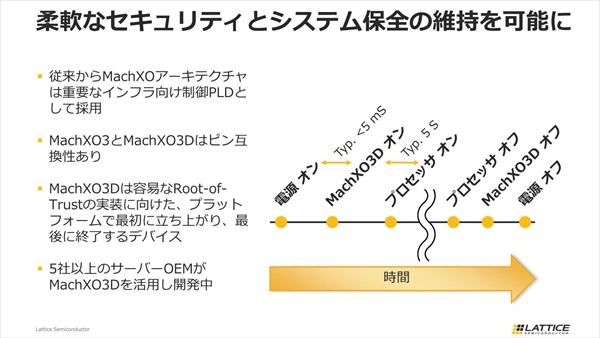

RoTの場合、システム内で最初に立ち上がり、最後に電源が切れるデバイスとなるため。これに必要な機能がすべて内蔵されているのが特徴である(Photo04)。

-

Photo04:サーバの制御用にすでに多くのMachXO3が利用されており、これをMachXO3Dに入れ替えるだけでセキュリティが強化できる(もちろんセキュリティ対策のコードを別に追加する必要はある)としている

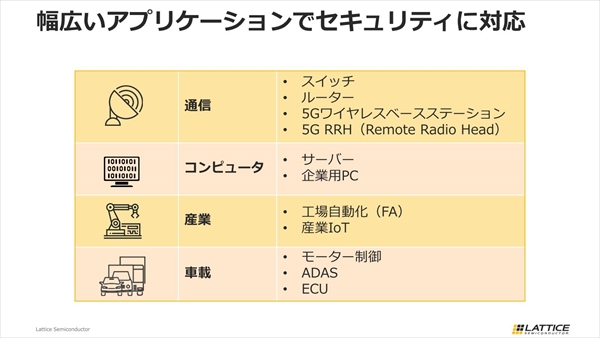

具体的にMachXO3Dがターゲットとしているのは、従来MachXO3が利用されてきた幅広いマーケット(Photo05)である。

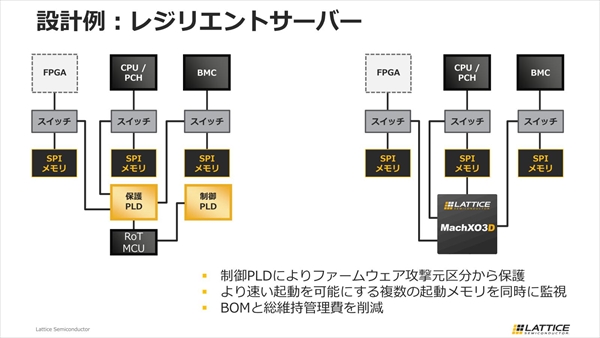

具体例としてはResilience Serverの実例(Photo06)が占めされた。ここではさまざまなコンポーネント向けの外付けSPI Flashを保護するという例で、基本的にはファームウェアアップデートを掛けるとき以外はSPI Flashに書き込みとか消去/初期化といった動作は発生しない。

逆にこれが発生するという事は、不正な動作となる。そこで、MachXO3DはCPUなりFPGAなりとSPIの通信を常時監視し(これは文字通り、SPIの信号をそのままマルチドロップ式にMachXO3Dで取り込む)、特定のコマンド列(それこそWriteだったりEraseだったり)を検出したら、ただちにスイッチをOffにするという制御を行うことで、SPI Flashへの攻撃を防げるという話であった。

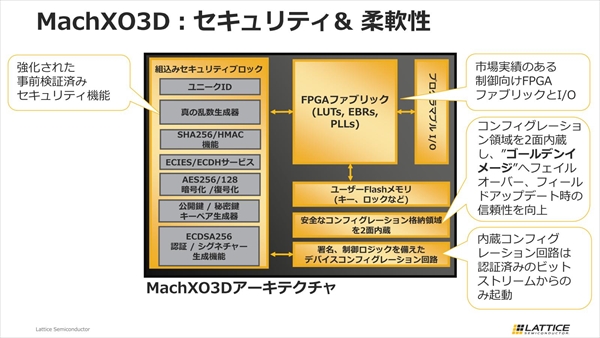

もちろんSPI Flashへの攻撃に先立ってMachXO3Dへ侵入されたら意味が無いので、MachXO3Dは強力な保護機能を搭載している。Photo07はその内部構造であるが、FPGA FabricとProgrammable I/OはMachXO3そのままである。

これにSecurity BlockとUser Flash、それとConfuguration Memoryを2 Bank搭載しているのが大きな特徴である。Configurationが2 BankあるのはFOTA Updateで失敗した場合への対策で、仮に失敗しても確実に動作する"Golden Image"を利用することでUpdate前の状況に戻せる、としている。ちなみにこのUser FlashとかConfiguration Memoryはすべてオンダイ構成になっており、外部のSPIなどを必要としない。このあたりはセキュリティを考えれば当然の配慮と言える。このMachXO3Dを利用することで、Photo02の問題に対して包括的なセキュリティを構築できる(Photo08)、という話であった。

-

Photo08:もちろんチップをMachXO3からMachXO3Dに変えるだけではだめで、その上で必要な機能を追加してやる必要があるから簡単とは言い難いのだが、少なくとも可能にする手段がこれで確保されたことになる

SensAIを10倍高速化させたSensAI 2.0

次いでSensAI 2.0について。SensAIそのものは昨年発表されたものであるが、今回はほぼ10倍高速化した(Photo09)とされた。

-

Photo09:ちなみに10倍の高速化であるが、層数の最適化などではなく、例えば内部のDSPが18bit×18bit動作だったものを9bit×9bitが2つにするといった、地道な最適化が行われたとの事

実際に動作デモも行われたが、ECP5にカメラ用のキャリアボードを搭載した評価キット(Photo10)を利用し、448×224pixel(内部的には224×224pixelを2領域として処理しているそうだ)の映像で人数カウントを行った(Photo11)場合、従来のSensAI 1.1(左)が1フレームあたり3秒近い処理時間が必要なのに対し、SensAI 2.0ではこれが300ms程度まで短縮できたとしている。

-

Photo10:これそのものはLatticeの「Embedded Vision Development Kit」である

-

Photo11:昨年の発表会では96×96pixelの画像で行ったが、今回は解像度を大幅に引き上げたために処理負荷が大分増えているとの事

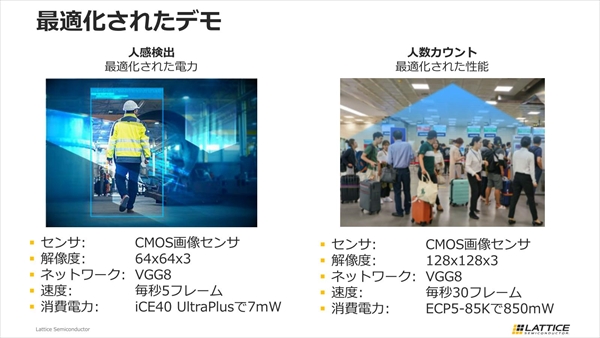

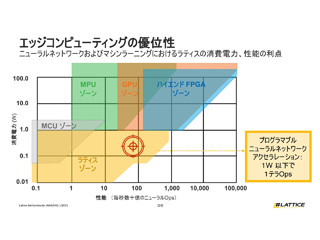

性能は精度とのバーターであるが、実際iCE40 UltraPlusとかECP5-85Kでの実績はこちら(Photo12)となっている。

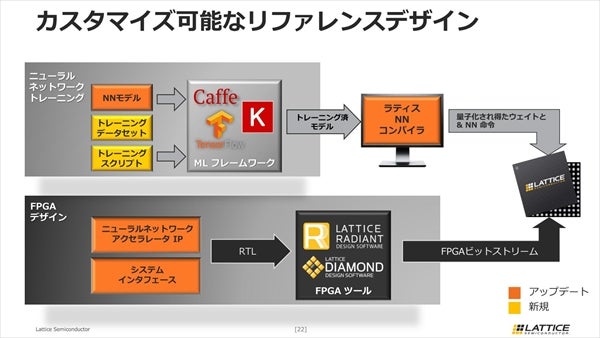

またリファレンスデザインにトレーニング用のデータセットとスクリプトが新たに追加された他、対応フレームワークにKerasが追加され(Photo13)、カスタムデザインサービスも4社増えて9社になった(Photo14)事が説明された。

-

Photo13:このトレーニング用のデータセットとかスクリプトは、ユーザーが自身でトレーニングデータをどう作るべきかの参考にするために追加されたそうだ

-

Photo14:昨年は5社であった。ちなみにpoco-apocoと三栄ハイテックスは日本企業である。これらのパートナーはFPGAのデザインだけでなく、MLのフレームワークとかアプリケーションの構築までカバーするとのこと